# LIGO Laboratory / LIGO Scientific Collaboration

# LIGO-T1000567-v1 Advanced LIGO UK

29 September 2010

**OMC Coil Driver Board Test Plan**

R. M. Cutler, University of Birmingham

Distribution of this document: Inform aligo\_sus

This is an internal working note of the Advanced LIGO Project, prepared by members of the UK team.

### **Institute for Gravitational Research University of Glasgow**

Phone +44 (0) 141 330 5884 Fax +44 (0) 141 330 6833

E-mail <u>k.strain@physics.gla.ac.uk</u> **Engineering Department**

**CCLRC Rutherford Appleton Laboratory** Phone +44 (0) 1235 445 297

Fax +44 (0) 1235 445 843 E-mail <u>J.Greenhalgh@rl.ac.uk</u>

# School of Physics and Astronomy University of Birmingham

Phone +44 (0) 121 414 6447 Fax +44 (0) 121 414 3722 E-mail av@star.sr.bham.ac.uk **Department of Physics**

**Department of Physics University of Strathclyde**Phone +44 (0) 1411 548 3360

Fax +44 (0) 141 552 2891

E-mail N.Lockerbie@phys.strath.ac.uk

http://www.ligo.caltech.edu/

http://www.physics.gla.ac.uk/igr/sus/

http://www.sr.bham.ac.uk/research/gravity/rh,d,2.html

http://www.eng-external.rl.ac.uk/advligo/papers\_public/ALUK\_Homepage.htm

# OMC COIL DRIVER BOARD TEST PLAN

| Unit | OMC | 10 | Serial No | <br> |

|------|-----|----|-----------|------|

|      | _   | -  |           |      |

|      |     | 10 |           |      |

### **Contents**

- 1. Description

- 2. Test Equipment

- 3. Inspection

- 4. Continuity Checks

- 5. Test Set Up

- 6. Power

- 7. Relay operation

- 8. Corner Frequency Tests

- 9. Monitor Outputs

- 10. Distortion

- 11. DC Stability

- 12. Crosstalk Tests

- 13. Dynamic range

### 1. Description

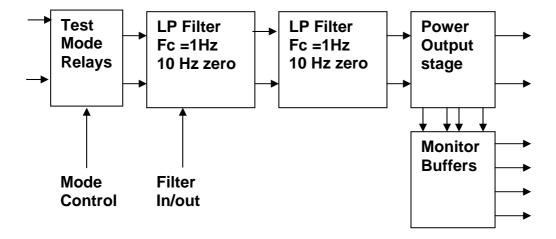

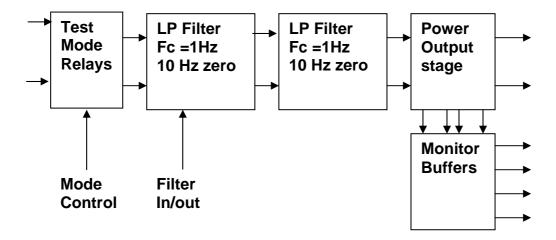

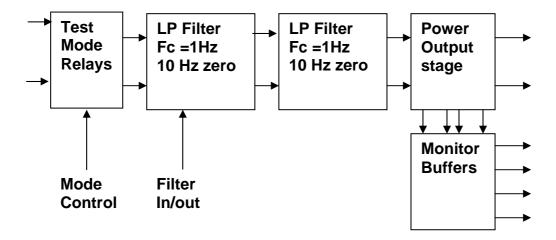

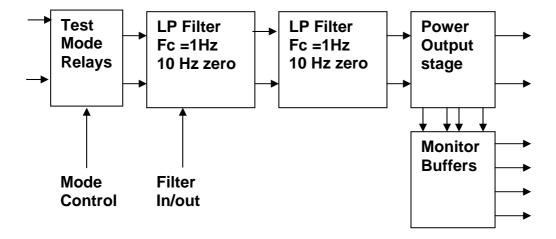

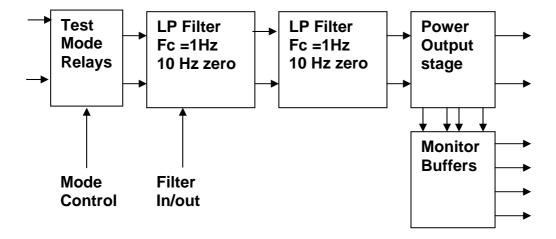

### **Block diagram**

### 2. Description

Each OMC Driver board consists of four identical channels and three power regulators, which provide regulated power to the four channels.

Taking the diagram block by block, the first block contains relays which switch the circuit between the normal inputs and the test inputs.

The second block contains a low pass filter with a corner frequency of 1 Hz, followed by a complimentary zero at 10 Hz. To a good approximation, the gain is reduced by a factor of 0.7 at 1 Hz, the attenuation increases at a rate of 20dB/decade up to the corner frequency of the zero at 10 Hz, after which the characteristic levels off. This filter may be switched in and out as required by relay control. Operational amplifiers follow which have a gain of 1.2.

The third block contains a filter with a similar characteristic, the main difference being that this filter is not switchable.

This is followed by the output buffer stage, consisting of an operational amplifier followed by a power driver buffer. The power driver is unity gain, and the operational amplifier provides the gain in this stage. The loop is closed around the buffer/operational amplifier pair. The current limit is set to 0.25A.

The outputs are buffered by unity gain voltage followers which drive the monitor board.

| Unit | OMC <sup>2</sup> | 10Serial No |

|------|------------------|-------------|

|      |                  |             |

| Date | 29/10/1          |             |

### 2. Test equipment

Power supplies (At least +/- 20v variable, 1A)

Signal generator (capable of delivering 10v peak, 0.1Hz to 10 KHz))

Digital oscilloscope

Analogue oscilloscope

Agilent Dynamic Signal Analyser (or similar)

Low noise Balanced Driver circuit

Relay test box

Record the Models and serial numbers of the test equipment used below.

| Unit (e.g. DVM)    | Manufacturer     | Model   | Serial Number |

|--------------------|------------------|---------|---------------|

| Signal Generator   | Agilent          | 33250A  |               |

| Oscilloscope       | ISO-TECH         | ISR622  |               |

| PSU*2              | Farnell          | L30-2   |               |

| DVM                | Fluke            | 77111   |               |

| Signal analyzer    | Agilent          | 35670A  |               |

| Pre-amplifier      | Stanford Systems | SR560   |               |

| DVM                | TENMA            | 72-7730 |               |

| V/I calibrator     | Time Electronics | 1044    |               |

| Function Generator | Hitachi          | VG-4429 |               |

| Unit | OMC 10   | .Serial No |

|------|----------|------------|

|      | Xen      |            |

| Date | 29/10/10 |            |

# 3. Inspection

### Workmanship

Inspect the general workmanship standard and comment:  $\sqrt{\phantom{a}}$

C21 and C26 have been replaced by a 10nF polypropylene capacitor on all channels.

C200 has been soldered across R5 and R23 on all channels.

### Links:

Check that links W4 and W5 are present on each channel. If not, connect them.

| Unit          | OMC 10.  | Serial No |

|---------------|----------|-----------|

| Test Engineer |          |           |

| Date          | 29/10/10 |           |

# 4. Continuity Checks

J2

| PIN | SIGNAL | DESCRIPTION   | To J1 PIN        | OK?       |

|-----|--------|---------------|------------------|-----------|

| 1   | PD1P   | Photodiode A+ | 1                | $\sqrt{}$ |

| 2   | PD2P   | Photodiode B+ | 2                | $\sqrt{}$ |

| 3   | PD3P   | Photodiode C+ | 3                | $\sqrt{}$ |

| 4   | PD4P   | Photodiode D+ | Photodiode D+ 4  |           |

|     | 5      | 0V            | $\sqrt{}$        |           |

| 6   | PD1N   | Photodiode A- | 14               |           |

| 7   | PD2N   | Photodiode B- | Photodiode B- 15 |           |

| 8   | PD3N   | Photodiode C- | Photodiode C- 16 |           |

| 9   | PD4N   | Photodiode D- | 17               |           |

**J5**

| PIN | SIGNAL |    | To J1 PIN | OK?      |

|-----|--------|----|-----------|----------|

| 1   | Imon1P |    | 5         | <b>√</b> |

| 2   | Imon2P |    | 6         | V        |

| 3   | Imon3P |    | 7         | V        |

| 4   | Imon4P |    | 8         | V        |

|     | 5      | 0V | V         |          |

| 6   | Imon1N |    | 18        | V        |

| 7   | Imon2N |    | 19        | V        |

| 8   | Imon3N |    | 20        | V        |

| 9   | Imon4N |    | 21        | V        |

# Power Supply to Satellite box J1

| PIN | SIGNAL   | DESCRIPTION | OK?          |

|-----|----------|-------------|--------------|

| 9   | V+ (TP1) | +17v Supply | V            |

| 10  | V+ (TP1) | +17v Supply | <b>√</b>     |

| 11  | V- (TP2) | -17v Supply | <b>√</b>     |

| 12  | V- (TP2) | -17v Supply | √            |

| 13  | 0V (TP3) |             | $\checkmark$ |

| 22  | 0V (TP3) |             |              |

| 23  | 0V (TP3) |             |              |

| 24  | 0V (TP3) |             |              |

| 25  | 0V (TP3) |             | <b>√</b>     |

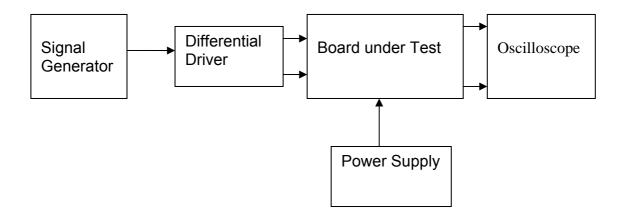

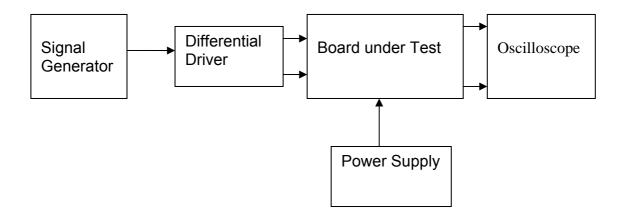

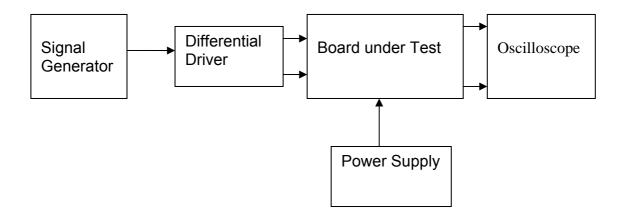

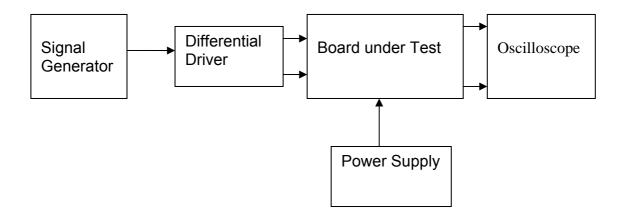

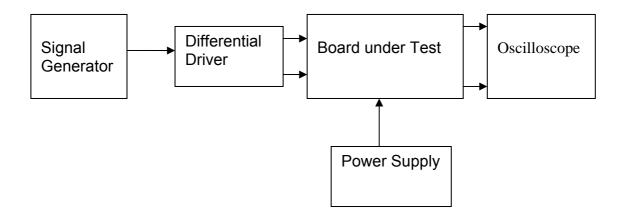

### 5. TEST SET UP

### Note:

- (1) Input signal to differential amplifier is generally stated in the tests below. There is therefore an inherent gain of 2 in the system.

- (2) Some signal generators will indicate 1vpk/pk when the output is in fact 1v Peak into the high impedance Differential driver used. The test procedure refers to the actual voltage out of the signal generator.

### **Connections:**

Differential signal inputs to the board under test:

J3 pins 1, 2,  $\overline{3}$ , 4 = positive input

J3 pins 6, 7, 8, 9 = negative input

J3 pin 5 = ground

#### Power

J1 pin 9, 10 = +16.5v

J1 pin 11,12 = -16.5

J1 pins 22, 23, 24, 25 = 0v

### Outputs

| Ch1- = J4 pin 9  |

|------------------|

| Ch2- = J4 pin 11 |

| Ch3- = J4 pin 13 |

| Ch4- = J4 pin 15 |

|                  |

| Unit | OMC 10   | Serial No |  |

|------|----------|-----------|--|

|      | Xen      |           |  |

| Date | 29/10/10 |           |  |

### 6. Power

# Check the polarity of the wiring:

### **3 Pin Power Connector**

Set the power supply outputs to zero.

Connect power to the unit

Increase the voltages on the supplies to +/-3V.

Determine that the supply polarities are correct on TP1 and TP2.

If they are, increase input voltages to +/- 16.5v.

Record the output voltages, measured on a 4 digit DVM, from each regulator Observe the output on an analogue oscilloscope, set to AC. Measure and record the peak to peak noise on each output.

Record regulator outputs:

| Regulator | Output voltage | Output noise | Nominal +/- 0.5v? |

|-----------|----------------|--------------|-------------------|

| +12v TP5  | 12.05          | 1mV          | $\sqrt{}$         |

| +15v TP4  | 14.93          | 1mV          | $\checkmark$      |

| -15v TP6  | -15.17         | 5mV          | $\checkmark$      |

| All Outputs smooth DC, no oscillation? | 1 |  |

|----------------------------------------|---|--|

|----------------------------------------|---|--|

Record Power Supply Currents

| Supply | Current |

|--------|---------|

| +16.5v | 350mA   |

| -16.5v | 250mA   |

If the supplies are correct, proceed to the next test.

| Unit | OMC 10   | Serial No |  |

|------|----------|-----------|--|

|      | Xen      |           |  |

| Date | 29/10/10 |           |  |

# 7. Relay Operation

Operate each relay in turn.

Observe its operation. LEDs should illuminate when the relays are operated.

### **Filter**

| Channel | Indi | Indicator |   |

|---------|------|-----------|---|

|         | ON   | OFF       |   |

| Ch1     | V    |           | V |

| Ch2     | V    |           | V |

| Ch3     | V    |           |   |

| Ch4     |      |           |   |

### **Test Switches**

| Channel | Indi     | Indicator |   |

|---------|----------|-----------|---|

|         | ON       | OFF       |   |

| Ch1     | V        |           | V |

| Ch2     | V        |           | V |

| Ch3     | V        |           | V |

| Ch4     | <b>√</b> |           |   |

| Unit          | $$ OMC $_{	t }$ | _10 | Serial No | <br> |

|---------------|-----------------|-----|-----------|------|

| Test Engineer | Xen             | _   |           |      |

| Date          | 29/10/          | /10 |           |      |

### 8. Corner frequency tests

Apply a signal to the input, amplitude 1v peak, Frequency 1Hz.

8.1 Both Filters out: Remove W4 and W5

Measure and record the Peak to Peak output between TP9 and TP13

at 1Hz, 10Hz and 100Hz for each channel

|     | 1Hz | 10Hz | 100Hz | Specification | Pass/Fail    |

|-----|-----|------|-------|---------------|--------------|

| Ch1 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\checkmark$ |

| Ch2 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\sqrt{}$    |

| Ch3 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\sqrt{}$    |

| Ch4 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | V            |

### **8.2** Switched filter in: Remove W5, insert W4

Switch in the filter and test the response at 0.1Hz, 1Hz, 10Hz, 100Hz, and 1KHz. Measure and record the Peak to Peak output between TP9 and TP13.

0.1Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 4.9    | 4.7 to 5v     | $\sqrt{}$ |

| Ch2 | 4.9    | 4.7 to 5v     | $\sqrt{}$ |

| Ch3 | 4.9    | 4.7 to 5v     | $\sqrt{}$ |

| Ch4 | 4.9    | 4.7 to 5v     | V         |

1Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 3.3    | 3.3v to 3.7v  | $\sqrt{}$ |

| Ch2 | 3.3    | 3.3v to 3.7v  | V         |

| Ch3 | 3.3    | 3.3v to 3.7v  | V         |

| Ch4 | 3.3    | 3.3v to 3.7v  | V         |

10Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 0.68   | 0.48 to 0.75v | $\checkmark$ |

| Ch2 | 0.68   | 0.48 to 0.75v | <b>√</b>     |

| Ch3 | 0.68   | 0.48 to 0.75v | <b>√</b>     |

| Ch4 | 0.68   | 0.48 to 0.75v | <b>√</b>     |

100Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 0.48   | 0.4v to 0.5v  | $\sqrt{}$ |

| Ch2 | 0.48   | 0.4v to 0.5v  | $\sqrt{}$ |

| Ch3 | 0.48   | 0.4v to 0.5v  | $\sqrt{}$ |

| Ch4 | 0.48   | 0.4v to 0.5v  | V         |

1 KHz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 0.47   | 0.4v to 0.5v  | V         |

| Ch2 | 0.47   | 0.4v to 0.5v  | V         |

| Ch3 | 0.47   | 0.4v to 0.5v  | V         |

| Ch4 | 0.47   | 0.4v to 0.5v  | <b>√</b>  |

| Unit          | OMC_10   | DSerial No |  |

|---------------|----------|------------|--|

| Test Engineer | Xen      |            |  |

| Date          | 29/10/10 | )          |  |

### **8.3** Fixed filter in: Remove W4, insert W5

Measure and record the peak to peak output between TP9 and TP13 at 0.1Hz. Repeat for 1Hz, 10Hz, 100Hz, and 1KHz.

### 0.1Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 4.85   | 4.7v to 5v    | V         |

| Ch2 | 4.85   | 4.7v to 5v    | V         |

| Ch3 | 4.85   | 4.7v to 5v    | √         |

| Ch4 | 4.85   | 4.7v to 5v    | √         |

#### 1Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 3.3    | 3v to 3.4v    | $\checkmark$ |

| Ch2 | 3.2    | 3v to 3.4v    | <b>√</b>     |

| Ch3 | 3.2    | 3v to 3.4v    | <b>√</b>     |

| Ch4 | 3.3    | 3v to 3.4v    | <b>√</b>     |

### 10Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 0.49   | 0.4v to 0.5v  | $\checkmark$ |

| Ch2 | 0.48   | 0.4v to 0.5v  |              |

| Ch3 | 0.48   | 0.4v to 0.5v  |              |

| Ch4 | 0.49   | 0.4v to 0.5v  |              |

### 100Hz

|     | Output | Specification  | Pass/Fail |

|-----|--------|----------------|-----------|

| Ch1 | 0.16   | 0.15v to 0.16v | V         |

| Ch2 | 0.16   | 0.15v to 0.16v | <b>√</b>  |

| Ch3 | 0.16   | 0.15v to 0.16v | <b>√</b>  |

| Ch4 | 0.16   | 0.15v to 0.16v | V         |

### 1 KHz

|     | Output | Specification  | Pass/Fail |

|-----|--------|----------------|-----------|

| Ch1 | 0.16   | 0.14v to 0.16v | V         |

| Ch2 | 0.16   | 0.14v to 0.16v | V         |

| Ch3 | 0.16   | 0.14v to 0.16v | V         |

| Ch4 | 0.16   | 0.14v to 0.16v | <b>√</b>  |

| Unit          | OMC_10   | .Serial No |

|---------------|----------|------------|

| Test Engineer | Xen      |            |

| Date          | 29/10/10 |            |

### 9. Monitor Outputs

Remove links W4 and W5.

Connect a 39 ohm dummy load to each channel.

Apply a 1V r.m.s input at 10Hz measured between TP10 and TP14, and record the differential output from each monitor pair on P1 for each channel. Compare them with the voltage outputs (TP9 to TP13).

### **Voltage monitors**

| Ch. | Nominal | Output<br>between<br>TP9 & TP13 | Monitor Pins<br>on P1 | Monitor<br>Voltage | Pass/Fail:<br>Equal?<br>(+/- 0.1v) |

|-----|---------|---------------------------------|-----------------------|--------------------|------------------------------------|

| 1   | 1.22V   | 1.22                            | Pin 1 to Pin 2        | 1.22               | √                                  |

| 2   | 1.22V   | 1.22                            | Pin 5 to Pin 6        | 1.22               | √                                  |

| 3   | 1.22V   | 1.22                            | Pin 9 to Pin 10       | 1.22               | √                                  |

| 4   | 1.22V   | 1.22                            | Pin 13 to Pin 14      | 1.22               | √                                  |

#### **Current monitors**

| Ch. | Nominal | Monitor Pins     | Monitor O/P | Pass/Fail:<br>Equal?<br>(+/- 0.1v) |

|-----|---------|------------------|-------------|------------------------------------|

| 1   | 0.08V   | Pin 3 to Pin 4   | 0.08        | $\sqrt{}$                          |

| 2   | 0.08V   | Pin 7 to Pin 8   | 0.08        |                                    |

| 3   | 0.08V   | Pin 11 to Pin 12 | 0.08        |                                    |

| 4   | 0.08V   | Pin 15 to Pin 16 | 0.08        |                                    |

### 10. Distortion

Filter out. Increase input voltage to 10v peak, f = 1KHz. Dummy 39 Ohm loads. Observe the voltage across each load with an oscilloscope.

|     | Distortion Free? |  |  |

|-----|------------------|--|--|

| Ch1 | $\sqrt{}$        |  |  |

| Ch2 | $\sqrt{}$        |  |  |

| Ch3 | $\sqrt{}$        |  |  |

| Ch4 | $\sqrt{}$        |  |  |

| Unit | OMC    | 10 | .Serial No | <br> |

|------|--------|----|------------|------|

|      |        |    |            |      |

| Date | 29/10/ | 10 |            |      |

### 11. DC Stability

Use the precision voltage source via a break out box on the input (J3). All filters off. Record the differential output voltage between TP7 and TP11. Check stability while slowly increasing the output voltage. (Link W2 in)

|      | J3 pins 1,6 |                    | J3 pins 2,7 |                    | J3 pins 3,8 |                    | J3 pins 4,9 |                    |

|------|-------------|--------------------|-------------|--------------------|-------------|--------------------|-------------|--------------------|

|      | Ch1<br>o/p  | Ch1<br>stable<br>? | Ch2<br>o/p  | Ch2<br>stable<br>? | Ch3 o/p     | Ch3<br>stable<br>? | Ch4<br>o/p  | Ch4<br>stable<br>? |

| -10v | -24.5       | V                  | -24.5       | V                  | -24.5       | V                  | -24.5       | V                  |

| -7v  | -17.4       | V                  | -17.4       | <b>V</b>           | -17.4       | <b>V</b>           | -17.4       | <b>√</b>           |

| -5v  | -12.5       | V                  | -12.5       |                    | -12.5       | V                  | -12.5       | $\sqrt{}$          |

| -1v  | -2.5        | $\sqrt{}$          | -2.5        | $\sqrt{}$          | -2.5        | $\sqrt{}$          | -2.5        | $\sqrt{}$          |

| 0v   | 0           | $\sqrt{}$          | 0           |                    | 0           | $\sqrt{}$          | 0           | $\sqrt{}$          |

| 1v   | 2.5         | V                  | 2.5         | V                  | 2.5         | V                  | 2.5         | V                  |

| 5v   | 12.2        | V                  | 12.2        | V                  | 12.2        | V                  | 12.2        | V                  |

| 7v   | 17.0        | V                  | 17.0        | V                  | 17.0        | V                  | 17.0        | V                  |

| 10v  | 24.5        | V                  | 24.5        | V                  | 24.5        | V                  | 24.5        | V                  |

| Unit          | Serial No |

|---------------|-----------|

| Test Engineer | •••       |

| Date          |           |

### 12. Crosstalk Tests

The purpose of these tests is to determine the level of crosstalk between each of the channels. As this is a lengthy test, and is mainly a function of board layout, it may be decided to perform the full test on a sample board only, and repeat the quick test on subsequent units.

#### 12.1 Full Test

As crosstalk is a function of board layout, this test is only necessary on a sample basis.

Use the HP Dynamic signal analyser to measure the cross talk between adjacent channels.

Apply the source, set at 1v r.m.s, to each channel in turn, via the differential driver, while grounding the inputs to adjacent channels.

Measure the transfer function to adjacent channels.

Record the maximum outputs on adjacent channels, and record the frequency at which this occurs. (Assuming an output signal is detectable).

| INPUT<br>CHANNEL | OUTPUT<br>CHANNEL | Output @<br>10Hz | Maximum<br>o/p | @<br>Frequency |

|------------------|-------------------|------------------|----------------|----------------|

| Channel 1        | Channel 2         |                  |                | -              |

| Channel 2        | Channel 1         |                  |                |                |

| Channel 2        | Channel 3         |                  |                |                |

| Channel 3        | Channel 2         |                  |                |                |

| Channel 3        | Channel 4         |                  |                |                |

| Channel 4        | Channel 3         |                  |                |                |

| Unit | OMC 10   | Serial No |  |

|------|----------|-----------|--|

|      | Xen      |           |  |

| Date | 29/10/10 |           |  |

### 13. Dynamic Range Tests

In this test, the board is tested at maximum dynamic range.

Connect a 39 Ohm load resistor to the output of each channel. Switch out the filters. Apply a 10v peak sinusoidal signal at 10 Hz to the input. Check that the signal on TP10 is 10v peak.

Observe the differential output voltage across the load resistors with an oscilloscope. Check that the waveforms are not clipping.

|           | Ch1          | Ch2      | Ch3          | Ch4 |

|-----------|--------------|----------|--------------|-----|

| Not       | $\checkmark$ | <b>√</b> | $\checkmark$ | V   |

| Clipping? |              |          |              |     |

|     | Theoretical o/p | Measured | OK+/- 0.1v? |

|-----|-----------------|----------|-------------|

| Ch1 | 1.12v           | 1.14     | $\sqrt{}$   |

| Ch2 | 1.12v           | 1.14     | V           |

| Ch3 | 1.12v           | 1.13     | V           |

| Ch4 | 1.12v           | 1.14     | V           |

# LIGO Laboratory / LIGO Scientific Collaboration

# LIGO-T1000567-v1 Advanced LIGO UK

29 September 2010

**OMC Coil Driver Board Test Plan**

R. M. Cutler, University of Birmingham

Distribution of this document: Inform aligo\_sus

This is an internal working note of the Advanced LIGO Project, prepared by members of the UK team.

### **Institute for Gravitational Research University of Glasgow**

Phone +44 (0) 141 330 5884 Fax +44 (0) 141 330 6833

E-mail <u>k.strain@physics.gla.ac.uk</u> **Engineering Department**

**CCLRC Rutherford Appleton Laboratory** Phone +44 (0) 1235 445 297

Fax +44 (0) 1235 445 843 E-mail <u>J.Greenhalgh@rl.ac.uk</u>

# School of Physics and Astronomy University of Birmingham

Phone +44 (0) 121 414 6447 Fax +44 (0) 121 414 3722 E-mail av@star.sr.bham.ac.uk **Department of Physics**

**Department of Physics University of Strathclyde**Phone +44 (0) 1411 548 3360

Fax +44 (0) 141 552 2891

E-mail N.Lockerbie@phys.strath.ac.uk

http://www.ligo.caltech.edu/

http://www.physics.gla.ac.uk/igr/sus/

http://www.sr.bham.ac.uk/research/gravity/rh,d,2.html

http://www.eng-external.rl.ac.uk/advligo/papers\_public/ALUK\_Homepage.htm

# OMC COIL DRIVER BOARD TEST PLAN

| Unit | OMC 2 | 2Serial No |  |

|------|-------|------------|--|

|      |       |            |  |

|      |       | 0          |  |

### **Contents**

- 1. Description

- 2. Test Equipment

- 3. Inspection

- 4. Continuity Checks

- 5. Test Set Up

- 6. Power

- 7. Relay operation

- 8. Corner Frequency Tests

- 9. Monitor Outputs

- 10. Distortion

- 11. DC Stability

- 12. Crosstalk Tests

- 13. Dynamic range

### 1. Description

### **Block diagram**

### 2. Description

Each OMC Driver board consists of four identical channels and three power regulators, which provide regulated power to the four channels.

Taking the diagram block by block, the first block contains relays which switch the circuit between the normal inputs and the test inputs.

The second block contains a low pass filter with a corner frequency of 1 Hz, followed by a complimentary zero at 10 Hz. To a good approximation, the gain is reduced by a factor of 0.7 at 1 Hz, the attenuation increases at a rate of 20dB/decade up to the corner frequency of the zero at 10 Hz, after which the characteristic levels off. This filter may be switched in and out as required by relay control. Operational amplifiers follow which have a gain of 1.2.

The third block contains a filter with a similar characteristic, the main difference being that this filter is not switchable.

This is followed by the output buffer stage, consisting of an operational amplifier followed by a power driver buffer. The power driver is unity gain, and the operational amplifier provides the gain in this stage. The loop is closed around the buffer/operational amplifier pair. The current limit is set to 0.25A.

The outputs are buffered by unity gain voltage followers which drive the monitor board.

| Unit | OMC    | 2Serial No |

|------|--------|------------|

|      | _      |            |

| Date | 27/10/ |            |

### 2. Test equipment

Power supplies (At least +/- 20v variable, 1A)

Signal generator (capable of delivering 10v peak, 0.1Hz to 10 KHz))

Digital oscilloscope

Analogue oscilloscope

Agilent Dynamic Signal Analyser (or similar)

Low noise Balanced Driver circuit

Relay test box

Record the Models and serial numbers of the test equipment used below.

| Unit (e.g. DVM)    | Manufacturer     | Model   | Serial Number |

|--------------------|------------------|---------|---------------|

| Signal Generator   | Agilent          | 33250A  |               |

| Oscilloscope       | ISO-TECH         | ISR622  |               |

| PSU*2              | Farnell          | L30-2   |               |

| DVM                | Fluke            | 77111   |               |

| Signal analyzer    | Agilent          | 35670A  |               |

| Pre-amplifier      | Stanford Systems | SR560   |               |

| DVM                | TENMA            | 72-7730 |               |

| V/I calibrator     | Time Electronics | 1044    |               |

| Function Generator | Hitachi          | VG-4429 |               |

| Unit | OMC 2 | Serial No |

|------|-------|-----------|

|      |       |           |

| Date |       |           |

# 3. Inspection

### Workmanship

Inspect the general workmanship standard and comment:  $\sqrt{\phantom{a}}$

C21 and C26 have been replaced by a 10nF polypropylene capacitor on all channels.

C200 has been soldered across R5 and R23 on all channels.

### Links:

Check that links W4 and W5 are present on each channel. If not, connect them.

| Unit          | OMC    | 2Serial No |

|---------------|--------|------------|

| Test Engineer | Xen    |            |

| Data          | 27/10/ |            |

# 4. Continuity Checks

J2

| PIN | SIGNA | L | DESCRIPTION  | ON         | To J1 PIN | OK?       |

|-----|-------|---|--------------|------------|-----------|-----------|

| 1   | PD1P  |   | Photodiode / | 4+         | 1         | $\sqrt{}$ |

| 2   | PD2P  |   | Photodiode I | 3+         | 2         | $\sqrt{}$ |

| 3   | PD3P  |   | Photodiode ( | C+         | 3         | $\sqrt{}$ |

| 4   | PD4P  |   | Photodiode I | <b>)</b> + | 4         |           |

|     | 5     |   | 0V           |            | $\sqrt{}$ |           |

| 6   | PD1N  |   | Photodiode / | ۹-         | 14        |           |

| 7   | PD2N  |   | Photodiode I | 3-         | 15        |           |

| 8   | PD3N  |   | Photodiode ( | C-         | 16        |           |

| 9   | PD4N  |   | Photodiode I | D-         | 17        |           |

**J5**

| PIN | SIGNAL |    | To J1 PIN | OK?      |

|-----|--------|----|-----------|----------|

| 1   | Imon1P |    | 5         | <b>√</b> |

| 2   | Imon2P |    | 6         | V        |

| 3   | Imon3P |    | 7         | V        |

| 4   | Imon4P |    | 8         | V        |

|     | 5      | 0V | V         |          |

| 6   | Imon1N |    | 18        | V        |

| 7   | Imon2N |    | 19        | V        |

| 8   | Imon3N |    | 20        | V        |

| 9   | Imon4N |    | 21        | V        |

# Power Supply to Satellite box J1

| PIN | SIGNAL   | DESCRIPTION | OK?          |

|-----|----------|-------------|--------------|

| 9   | V+ (TP1) | +17v Supply | V            |

| 10  | V+ (TP1) | +17v Supply | <b>√</b>     |

| 11  | V- (TP2) | -17v Supply | <b>√</b>     |

| 12  | V- (TP2) | -17v Supply | √            |

| 13  | 0V (TP3) |             | $\checkmark$ |

| 22  | 0V (TP3) |             |              |

| 23  | 0V (TP3) |             |              |

| 24  | 0V (TP3) |             |              |

| 25  | 0V (TP3) |             | <b>√</b>     |

### 5. TEST SET UP

### Note:

- (1) Input signal to differential amplifier is generally stated in the tests below. There is therefore an inherent gain of 2 in the system.

- (2) Some signal generators will indicate 1vpk/pk when the output is in fact 1v Peak into the high impedance Differential driver used. The test procedure refers to the actual voltage out of the signal generator.

### **Connections:**

Differential signal inputs to the board under test:

J3 pins 1, 2,  $\overline{3}$ , 4 = positive input

J3 pins 6, 7, 8, 9 = negative input

J3 pin 5 = ground

#### Power

J1 pin 9, 10 = +16.5v

J1 pin 11,12 = -16.5

J1 pins 22, 23, 24, 25 = 0v

### Outputs

| Ch1- = J4 pin 9  |

|------------------|

| Ch2- = J4 pin 11 |

| Ch3- = J4 pin 13 |

| Ch4- = J4 pin 15 |

|                  |

| Unit | OMC 2    | Serial No |

|------|----------|-----------|

|      | Xen      |           |

| •    | 27/10/10 |           |

### 6. Power

### Check the polarity of the wiring:

### **3 Pin Power Connector**

Set the power supply outputs to zero.

Connect power to the unit

Increase the voltages on the supplies to +/-3V.

Determine that the supply polarities are correct on TP1 and TP2.

If they are, increase input voltages to +/- 16.5v.

Record the output voltages, measured on a 4 digit DVM, from each regulator Observe the output on an analogue oscilloscope, set to AC. Measure and record the peak to peak noise on each output.

Record regulator outputs:

| Regulator | Output voltage | Output noise | Nominal<br>+/- 0.5v? |

|-----------|----------------|--------------|----------------------|

| +12v TP5  | 11.99          | 1mV          |                      |

| +15v TP4  | 14.96          | 1mV          |                      |

| -15v TP6  | -15.02         | 5mV          | <b>√</b>             |

| All Outputs smooth DC, no oscillation? | 1 |  |

|----------------------------------------|---|--|

|----------------------------------------|---|--|

Record Power Supply Currents

| Supply | Current |

|--------|---------|

| +16.5v | 250mA   |

| -16.5v | 350mA   |

If the supplies are correct, proceed to the next test.

| Unit | OMC 2.   | Serial No |

|------|----------|-----------|

|      |          |           |

| Date | 27/10/10 |           |

# 7. Relay Operation

Operate each relay in turn.

Observe its operation. LEDs should illuminate when the relays are operated.

### **Filter**

| Channel | Indi | Indicator |   |

|---------|------|-----------|---|

|         | ON   | OFF       |   |

| Ch1     | V    |           | V |

| Ch2     | V    |           | V |

| Ch3     | V    |           |   |

| Ch4     |      |           |   |

### **Test Switches**

| Channel | Indicator |     | OK?       |

|---------|-----------|-----|-----------|

|         | ON        | OFF |           |

| Ch1     | V         |     | V         |

| Ch2     | V         |     | V         |

| Ch3     | V         |     | V         |

| Ch4     | <b>√</b>  |     | $\sqrt{}$ |

| Unit          | OMC_   | 2Serial No |

|---------------|--------|------------|

| Test Engineer | Xen    | ••••••     |

| Date          | 27/10/ | 10         |

### 8. Corner frequency tests

Apply a signal to the input, amplitude 1v peak, Frequency 1Hz.

8.1 Both Filters out: Remove W4 and W5

Measure and record the Peak to Peak output between TP9 and TP13

at 1Hz, 10Hz and 100Hz for each channel

|     | 1Hz | 10Hz | 100Hz | Specification | Pass/Fail    |

|-----|-----|------|-------|---------------|--------------|

| Ch1 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\checkmark$ |

| Ch2 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\sqrt{}$    |

| Ch3 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\sqrt{}$    |

| Ch4 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | V            |

### **8.2** Switched filter in: Remove W5, insert W4

Switch in the filter and test the response at 0.1Hz, 1Hz, 10Hz, 100Hz, and 1KHz. Measure and record the Peak to Peak output between TP9 and TP13.

0.1Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 4.9    | 4.7 to 5v     | $\sqrt{}$ |

| Ch2 | 4.9    | 4.7 to 5v     | $\sqrt{}$ |

| Ch3 | 4.9    | 4.7 to 5v     | $\sqrt{}$ |

| Ch4 | 4.9    | 4.7 to 5v     | V         |

1Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 3.4    | 3.3v to 3.7v  | $\checkmark$ |

| Ch2 | 3.4    | 3.3v to 3.7v  | V            |

| Ch3 | 3.4    | 3.3v to 3.7v  | V            |

| Ch4 | 3.4    | 3.3v to 3.7v  | V            |

10Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 0.68   | 0.48 to 0.75v | $\checkmark$ |

| Ch2 | 0.68   | 0.48 to 0.75v | <b>√</b>     |

| Ch3 | 0.68   | 0.48 to 0.75v | <b>√</b>     |

| Ch4 | 0.68   | 0.48 to 0.75v | <b>√</b>     |

100Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Ch2 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Ch3 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Ch4 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

1 kHz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 0.48   | 0.4v to 0.5v  | V         |

| Ch2 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Ch3 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Ch4 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Unit          | OMC_   | 2Serial No |

|---------------|--------|------------|

| Test Engineer | Xen    |            |

| Date          | 27/10/ | 10         |

### **8.3** Fixed filter in: Remove W4, insert W5

Measure and record the peak to peak output between TP9 and TP13 at 0.1Hz. Repeat for 1Hz, 10Hz, 100Hz, and 1KHz.

### 0.1Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 4.9    | 4.7v to 5v    | $\sqrt{}$ |

| Ch2 | 4.9    | 4.7v to 5v    | $\sqrt{}$ |

| Ch3 | 4.9    | 4.7v to 5v    | V         |

| Ch4 | 4.9    | 4.7v to 5v    | V         |

#### 1Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 3.3    | 3v to 3.4v    | $\checkmark$ |

| Ch2 | 3.3    | 3v to 3.4v    | V            |

| Ch3 | 3.3    | 3v to 3.4v    | V            |

| Ch4 | 3.3    | 3v to 3.4v    | <b>√</b>     |

### 10Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 0.48   | 0.4v to 0.5v  | $\checkmark$ |

| Ch2 | 0.48   | 0.4v to 0.5v  | √            |

| Ch3 | 0.48   | 0.4v to 0.5v  | √            |

| Ch4 | 0.48   | 0.4v to 0.5v  | <b>√</b>     |

### 100Hz

|     | Output | Specification  | Pass/Fail |

|-----|--------|----------------|-----------|

| Ch1 | 0.16   | 0.15v to 0.16v | V         |

| Ch2 | 0.16   | 0.15v to 0.16v | <b>√</b>  |

| Ch3 | 0.16   | 0.15v to 0.16v | <b>√</b>  |

| Ch4 | 0.16   | 0.15v to 0.16v | V         |

### 1 kHz

|     | Output | Specification  | Pass/Fail |

|-----|--------|----------------|-----------|

| Ch1 | 0.16   | 0.14v to 0.16v | V         |

| Ch2 | 0.16   | 0.14v to 0.16v | V         |

| Ch3 | 0.16   | 0.14v to 0.16v | V         |

| Ch4 | 0.16   | 0.14v to 0.16v | <b>√</b>  |

| Unit          | OMC    | 2Serial No |

|---------------|--------|------------|

| Test Engineer | Xen    |            |

| Date          | 27/10/ | 10         |

### 9. Monitor Outputs

Remove links W4 and W5.

Connect a 39 ohm dummy load to each channel.

Apply a 1V r.m.s input at 10Hz measured between TP10 and TP14, and record the differential output from each monitor pair on P1 for each channel. Compare them with the voltage outputs (TP9 to TP13).

### **Voltage monitors**

| Ch. | Nominal | Output<br>between<br>TP9 & TP13 | Monitor Pins<br>on P1 | Monitor<br>Voltage | Pass/Fail:<br>Equal?<br>(+/- 0.1v) |

|-----|---------|---------------------------------|-----------------------|--------------------|------------------------------------|

| 1   | 1.22V   | 1.22                            | Pin 1 to Pin 2        | 1.22               | $\checkmark$                       |

| 2   | 1.22V   | 1.22                            | Pin 5 to Pin 6        | 1.22               | $\checkmark$                       |

| 3   | 1.22V   | 1.22                            | Pin 9 to Pin 10       | 1.22               | V                                  |

| 4   | 1.22V   | 1.22                            | Pin 13 to Pin 14      | 1.22               | $\checkmark$                       |

#### **Current monitors**

| Ch. | Nominal | Monitor Pins     | Monitor O/P | Pass/Fail:<br>Equal?<br>(+/- 0.1v) |

|-----|---------|------------------|-------------|------------------------------------|

| 1   | 0.08V   | Pin 3 to Pin 4   | 0.08        | $\sqrt{}$                          |

| 2   | 0.08V   | Pin 7 to Pin 8   | 0.08        |                                    |

| 3   | 0.08V   | Pin 11 to Pin 12 | 0.08        |                                    |

| 4   | 0.08V   | Pin 15 to Pin 16 | 0.08        |                                    |

### 10. Distortion

Filter out. Increase input voltage to 10v peak, f = 1kHz. Dummy 39 Ohm loads. Observe the voltage across each load with an oscilloscope.

|     | Distortion Free? |  |

|-----|------------------|--|

| Ch1 | $\sqrt{}$        |  |

| Ch2 | $\sqrt{}$        |  |

| Ch3 | $\sqrt{}$        |  |

| Ch4 | $\sqrt{}$        |  |

| Unit          | OMC_2.   | Serial No |

|---------------|----------|-----------|

| Test Engineer | Xen      |           |

| Date          | 27/10/10 |           |

### 11. DC Stability

Use the precision voltage source via a break out box on the input (J3). All filters off. Record the differential output voltage between TP7 and TP11. Check stability while slowly increasing the output voltage. (Link W2 in)

|      | J3 pins 1,6 |                    | J3 pins 2,7 |                    | J3 pins 3,8 |                    | J3 pins 4,9 |                    |

|------|-------------|--------------------|-------------|--------------------|-------------|--------------------|-------------|--------------------|

|      | Ch1<br>o/p  | Ch1<br>stable<br>? | Ch2<br>o/p  | Ch2<br>stable<br>? | Ch3 o/p     | Ch3<br>stable<br>? | Ch4<br>o/p  | Ch4<br>stable<br>? |

| -10v | -24.5       | $\sqrt{}$          | -24.5       | $\sqrt{}$          | -24.5       | $\sqrt{}$          | -24.5       | $\sqrt{}$          |

| -7v  | -17.4       | <b>V</b>           | -17.3       | V                  | -17.4       | V                  | -17.4       | V                  |

| -5v  | -12.5       | <b>V</b>           | -12.5       | V                  | -12.5       | V                  | -12.5       | V                  |

| -1v  | -2.5        | $\sqrt{}$          | -2.4        | $\sqrt{}$          | -2.4        | $\sqrt{}$          | -2.5        | $\sqrt{}$          |

| 0v   | 0           | $\checkmark$       | 0           | $\sqrt{}$          | 0           | $\checkmark$       | 0           | $\sqrt{}$          |

| 1v   | 2.5         | <b>V</b>           | 2.4         | V                  | 2.4         | <b>V</b>           | 2.4         | V                  |

| 5v   | 12.3        | V                  | 12.3        | V                  | 12.4        | V                  | 12.4        | V                  |

| 7v   | 17.0        | V                  | 17.0        | V                  | 17.2        | V                  | 17.2        | V                  |

| 10v  | 24.5        | V                  | 24.5        | V                  | 24.5        | V                  | 24.5        | V                  |

| Unit          | .Serial No |

|---------------|------------|

| Test Engineer | •••        |

| Date          |            |

#### 12. Crosstalk Tests

The purpose of these tests is to determine the level of crosstalk between each of the channels. As this is a lengthy test, and is mainly a function of board layout, it may be decided to perform the full test on a sample board only, and repeat the quick test on subsequent units.

#### 12.1 Full Test

As crosstalk is a function of board layout, this test is only necessary on a sample basis.

Use the HP Dynamic signal analyser to measure the cross talk between adjacent channels.

Apply the source, set at 1v r.m.s, to each channel in turn, via the differential driver, while grounding the inputs to adjacent channels.

Measure the transfer function to adjacent channels.

Record the maximum outputs on adjacent channels, and record the frequency at which this occurs. (Assuming an output signal is detectable).

| INPUT<br>CHANNEL | OUTPUT<br>CHANNEL | Maximum<br>Output | @ Frequency |

|------------------|-------------------|-------------------|-------------|

| Channel 1        | Channel 2         |                   |             |

| Channel 2        | Channel 1         |                   |             |

| Channel 2        | Channel 3         |                   |             |

| Channel 3        | Channel 2         |                   |             |

| Channel 3        | Channel 4         |                   |             |

| Channel 4        | Channel 3         |                   |             |

| Unit | OMC 2 | Serial No |

|------|-------|-----------|

|      |       |           |

| •    |       |           |

# 13. Dynamic Range Tests

In this test, the board is tested at maximum dynamic range.

Connect a 39 Ohm load resistor to the output of each channel. Switch out the filters. Apply a 10v peak sinusoidal signal at 10 Hz to the input. Check that the signal on TP10 is 10v peak.

Observe the differential output voltage across the load resistors with an oscilloscope. Check that the waveforms are not clipping.

|           | Ch1          | Ch2      | Ch3          | Ch4 |

|-----------|--------------|----------|--------------|-----|

| Not       | $\checkmark$ | <b>√</b> | $\checkmark$ | V   |

| Clipping? |              |          |              |     |

|     | Theoretical o/p | Measured | OK+/- 0.1v? |

|-----|-----------------|----------|-------------|

| Ch1 | 1.12v           | 1.13     | $\sqrt{}$   |

| Ch2 | 1.12v           | 1.13     | V           |

| Ch3 | 1.12v           | 1.13     | √           |

| Ch4 | 1.12v           | 1.14     | V           |

# LIGO Laboratory / LIGO Scientific Collaboration

# LIGO-T1000567-v1 Advanced LIGO UK

29 September 2010

**OMC Coil Driver Board Test Plan**

R. M. Cutler, University of Birmingham

Distribution of this document: Inform aligo\_sus

This is an internal working note of the Advanced LIGO Project, prepared by members of the UK team.

### **Institute for Gravitational Research University of Glasgow**

Phone +44 (0) 141 330 5884 Fax +44 (0) 141 330 6833

E-mail <u>k.strain@physics.gla.ac.uk</u> **Engineering Department**

**CCLRC Rutherford Appleton Laboratory** Phone +44 (0) 1235 445 297

Fax +44 (0) 1235 445 843 E-mail <u>J.Greenhalgh@rl.ac.uk</u>

# School of Physics and Astronomy University of Birmingham

Phone +44 (0) 121 414 6447 Fax +44 (0) 121 414 3722 E-mail av@star.sr.bham.ac.uk **Department of Physics**

**Department of Physics University of Strathclyde**Phone +44 (0) 1411 548 3360

Fax +44 (0) 141 552 2891

E-mail N.Lockerbie@phys.strath.ac.uk

http://www.ligo.caltech.edu/

http://www.physics.gla.ac.uk/igr/sus/

http://www.sr.bham.ac.uk/research/gravity/rh,d,2.html

http://www.eng-external.rl.ac.uk/advligo/papers\_public/ALUK\_Homepage.htm

# OMC COIL DRIVER BOARD TEST PLAN

| Unit | OMC 3    | Serial No |

|------|----------|-----------|

|      | Xen      |           |

| •    | 27/10/10 |           |

### **Contents**

- 1. Description

- 2. Test Equipment

- 3. Inspection

- 4. Continuity Checks

- 5. Test Set Up

- 6. Power

- 7. Relay operation

- 8. Corner Frequency Tests

- 9. Monitor Outputs

- 10. Distortion

- 11. DC Stability

- 12. Crosstalk Tests

- 13. Dynamic range

### 1. Description

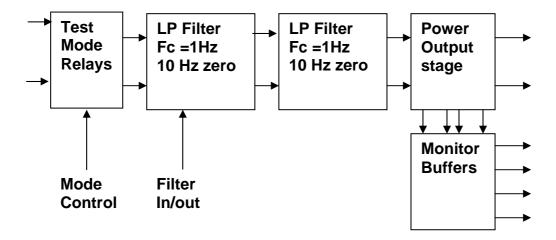

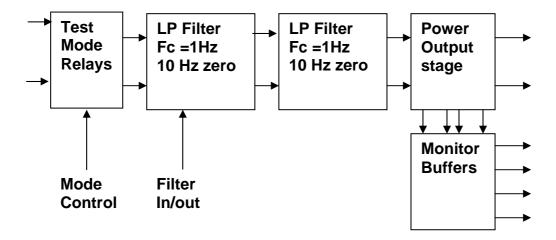

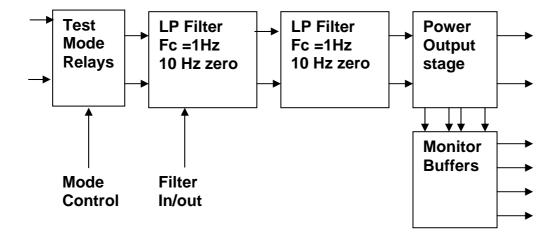

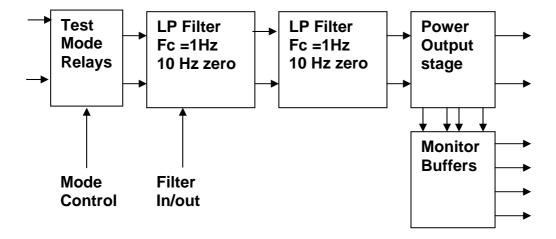

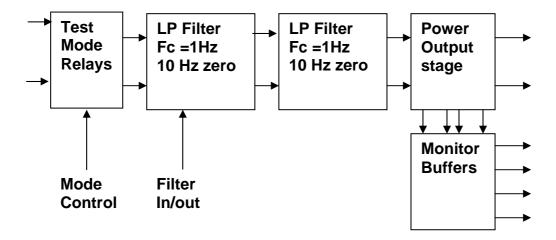

### **Block diagram**

### 2. Description

Each OMC Driver board consists of four identical channels and three power regulators, which provide regulated power to the four channels.

Taking the diagram block by block, the first block contains relays which switch the circuit between the normal inputs and the test inputs.

The second block contains a low pass filter with a corner frequency of 1 Hz, followed by a complimentary zero at 10 Hz. To a good approximation, the gain is reduced by a factor of 0.7 at 1 Hz, the attenuation increases at a rate of 20dB/decade up to the corner frequency of the zero at 10 Hz, after which the characteristic levels off. This filter may be switched in and out as required by relay control. Operational amplifiers follow which have a gain of 1.2.

The third block contains a filter with a similar characteristic, the main difference being that this filter is not switchable.

This is followed by the output buffer stage, consisting of an operational amplifier followed by a power driver buffer. The power driver is unity gain, and the operational amplifier provides the gain in this stage. The loop is closed around the buffer/operational amplifier pair. The current limit is set to 0.25A.

The outputs are buffered by unity gain voltage followers which drive the monitor board.

| Unit | OMC     | 3Serial No |

|------|---------|------------|

|      |         |            |

| Date | 27/10/1 | 0          |

### 2. Test equipment

Power supplies (At least +/- 20v variable, 1A)

Signal generator (capable of delivering 10v peak, 0.1Hz to 10 KHz))

Digital oscilloscope

Analogue oscilloscope

Agilent Dynamic Signal Analyser (or similar)

Low noise Balanced Driver circuit

Relay test box

Record the Models and serial numbers of the test equipment used below.

| Unit (e.g. DVM)    | Manufacturer     | Model   | Serial Number |

|--------------------|------------------|---------|---------------|

| Signal Generator   | Agilent          | 33250A  |               |

| Oscilloscope       | ISO-TECH         | ISR622  |               |

| PSU*2              | Farnell          | L30-2   |               |

| DVM                | Fluke            | 77111   |               |

| Signal analyzer    | Agilent          | 35670A  |               |

| Pre-amplifier      | Stanford Systems | SR560   |               |

| DVM                | TENMA            | 72-7730 |               |

| V/I calibrator     | Time Electronics | 1044    |               |

| Function Generator | Hitachi          | VG-4429 |               |

| Unit | OMC 3    | Serial No |

|------|----------|-----------|

|      | Xen      |           |

| Date | 27/10/10 |           |

# 3. Inspection

### Workmanship

Inspect the general workmanship standard and comment:  $\sqrt{\phantom{a}}$

C21 and C26 have been replaced by a 10nF polypropylene capacitor on all channels.

C200 has been soldered across R5 and R23 on all channels.

### Links:

Check that links W4 and W5 are present on each channel. If not, connect them.

| Unit          | OMC 3    | Serial No |  |

|---------------|----------|-----------|--|

| Test Engineer | Xen      |           |  |

| Date          | 27/10/10 |           |  |

# 4. Continuity Checks

# J2

| PIN | SIGNAL | DESCRIPTION     | To J1 PIN | OK?       |

|-----|--------|-----------------|-----------|-----------|

| 1   | PD1P   | Photodiode A+ 1 |           | $\sqrt{}$ |

| 2   | PD2P   | Photodiode B+   | 2         | $\sqrt{}$ |

| 3   | PD3P   | Photodiode C+   | 3         | $\sqrt{}$ |

| 4   | PD4P   | Photodiode D+   | 4         | $\sqrt{}$ |

|     | 5      | 0V              | $\sqrt{}$ |           |

| 6   | PD1N   | Photodiode A-   | 14        | $\sqrt{}$ |

| 7   | PD2N   | Photodiode B-   | 15        | $\sqrt{}$ |

| 8   | PD3N   | Photodiode C-   | 16        |           |

| 9   | PD4N   | Photodiode D-   | 17        |           |

### **J5**

| PIN | SIGNAL |    | To J1 PIN | OK?          |

|-----|--------|----|-----------|--------------|

| 1   | Imon1P |    | 5         | $\checkmark$ |

| 2   | Imon2P |    | 6         | V            |

| 3   | Imon3P |    | 7         | V            |

| 4   | Imon4P |    | 8         | V            |

|     | 5      | 0V | V         |              |

| 6   | Imon1N |    | 18        | V            |

| 7   | Imon2N |    | 19        | V            |

| 8   | Imon3N |    | 20        | V            |

| 9   | Imon4N |    | 21        | <b>√</b>     |

# Power Supply to Satellite box J1

| PIN | SIGNAL   | DESCRIPTION | OK?          |

|-----|----------|-------------|--------------|

| 9   | V+ (TP1) | +17v Supply | $\checkmark$ |

| 10  | V+ (TP1) | +17v Supply | <b>√</b>     |

| 11  | V- (TP2) | -17v Supply | <b>√</b>     |

| 12  | V- (TP2) | -17v Supply | <b>√</b>     |

| 13  | 0V (TP3) |             | V            |

| 22  | 0V (TP3) |             | √            |

| 23  | 0V (TP3) |             | <b>√</b>     |

| 24  | 0V (TP3) |             | √            |

| 25  | 0V (TP3) |             | <b>√</b>     |

#### 5. TEST SET UP

#### Note:

- (1) Input signal to differential amplifier is generally stated in the tests below. There is therefore an inherent gain of 2 in the system.

- (2) Some signal generators will indicate 1vpk/pk when the output is in fact 1v Peak into the high impedance Differential driver used. The test procedure refers to the actual voltage out of the signal generator.

#### **Connections:**

Differential signal inputs to the board under test:

J3 pins 1, 2,  $\overline{3}$ , 4 = positive input

J3 pins 6, 7, 8, 9 = negative input

J3 pin 5 = ground

#### Power

J1 pin 9, 10 = +16.5v

J1 pin 11,12 = -16.5

J1 pins 22, 23, 24, 25 = 0v

#### Outputs

| Ch1- = J4 pin 9  |

|------------------|

| Ch2- = J4 pin 11 |

| Ch3- = J4 pin 13 |

| Ch4- = J4 pin 15 |

|                  |

| Unit | OMC 3    | Serial No |

|------|----------|-----------|

|      | Xen      |           |

| •    | 27/10/10 |           |

#### 6. Power

# Check the polarity of the wiring:

#### **3 Pin Power Connector**

Set the power supply outputs to zero.

Connect power to the unit

Increase the voltages on the supplies to +/-3V.

Determine that the supply polarities are correct on TP1 and TP2.

If they are, increase input voltages to +/- 16.5v.

Record the output voltages, measured on a 4 digit DVM, from each regulator Observe the output on an analogue oscilloscope, set to AC. Measure and record the peak to peak noise on each output.

Record regulator outputs:

| Regulator | Output voltage | Output noise | Nominal<br>+/- 0.5v? |

|-----------|----------------|--------------|----------------------|

| +12v TP5  | 12.11          | 1mV          |                      |

| +15v TP4  | 14.94          | 1mV          |                      |

| -15v TP6  | -15.07         | 5mV          | <b>√</b>             |

| All Outputs smooth DC, no oscillation? | 1 |  |

|----------------------------------------|---|--|

|----------------------------------------|---|--|

**Record Power Supply Currents**

| Supply | Current |

|--------|---------|

| +16.5v | 350mA   |

| -16.5v | 250mA   |

If the supplies are correct, proceed to the next test.

| Unit | OMC 3    | Serial No |

|------|----------|-----------|

|      |          |           |

| Date | 27/10/10 |           |

# 7. Relay Operation

Operate each relay in turn.

Observe its operation. LEDs should illuminate when the relays are operated.

#### **Filter**

| Channel | Indi | Indicator |   |

|---------|------|-----------|---|

|         | ON   | OFF       |   |

| Ch1     | V    |           | V |

| Ch2     | V    |           | V |

| Ch3     | V    |           |   |

| Ch4     |      |           |   |

#### **Test Switches**

| Channel | Indi     | Indicator |   |

|---------|----------|-----------|---|

|         | ON       | OFF       |   |

| Ch1     | V        |           | V |

| Ch2     | V        |           | V |

| Ch3     | V        |           | V |

| Ch4     | <b>√</b> |           |   |

| Unit           | OMC_3    | Serial No |

|----------------|----------|-----------|

| Test Engineer. | Xen      |           |

| Date           | 27/10/10 |           |

#### 8. Corner frequency tests

Apply a signal to the input, amplitude 1v peak, Frequency 1Hz.

8.1 Both Filters out: Remove W4 and W5

Measure and record the Peak to Peak output between TP9 and TP13

at 1Hz, 10Hz and 100Hz for each channel

|     | 1Hz | 10Hz | 100Hz | Specification | Pass/Fail    |

|-----|-----|------|-------|---------------|--------------|

| Ch1 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\checkmark$ |

| Ch2 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\sqrt{}$    |

| Ch3 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | $\sqrt{}$    |

| Ch4 | 4.9 | 5.0  | 5.0   | 4.7v to 5v    | V            |

#### **8.2** Switched filter in: Remove W5, insert W4

Switch in the filter and test the response at 0.1Hz, 1Hz, 10Hz, 100Hz, and 1KHz. Measure and record the Peak to Peak output between TP9 and TP13.

0.1Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 4.9    | 4.7 to 5v     | $\checkmark$ |

| Ch2 | 4.9    | 4.7 to 5v     | $\checkmark$ |

| Ch3 | 4.9    | 4.7 to 5v     | $\checkmark$ |

| Ch4 | 4.9    | 4.7 to 5v     | $\checkmark$ |

1Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 3.4    | 3.3v to 3.7v  | $\sqrt{}$ |

| Ch2 | 3.4    | 3.3v to 3.7v  | V         |

| Ch3 | 3.4    | 3.3v to 3.7v  | V         |

| Ch4 | 3.4    | 3.3v to 3.7v  | V         |

10Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 0.68   | 0.48 to 0.75v | $\checkmark$ |

| Ch2 | 0.68   | 0.48 to 0.75v | V            |

| Ch3 | 0.68   | 0.48 to 0.75v | V            |

| Ch4 | 0.68   | 0.48 to 0.75v | <b>√</b>     |

100Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 0.48   | 0.4v to 0.5v  | √         |

| Ch2 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Ch3 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

| Ch4 | 0.48   | 0.4v to 0.5v  | <b>√</b>  |

1 KHz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 0.47   | 0.4v to 0.5v  | <b>√</b>  |

| Ch2 | 0.47   | 0.4v to 0.5v  | V         |

| Ch3 | 0.47   | 0.4v to 0.5v  | V         |

| Ch4 | 0.47   | 0.4v to 0.5v  | <b>√</b>  |

| Unit          | OMC_3    | Serial No |  |

|---------------|----------|-----------|--|

| Test Engineer | Xen      |           |  |

| Date          | 27/10/10 |           |  |

#### **8.3** Fixed filter in: Remove W4, insert W5

Measure and record the peak to peak output between TP9 and TP13 at 0.1Hz. Repeat for 1Hz, 10Hz, 100Hz, and 1KHz.

#### 0.1Hz

|     | Output | Specification | Pass/Fail |

|-----|--------|---------------|-----------|

| Ch1 | 4.85   | 4.7v to 5v    | V         |

| Ch2 | 4.85   | 4.7v to 5v    | V         |

| Ch3 | 4.85   | 4.7v to 5v    | √         |

| Ch4 | 4.85   | 4.7v to 5v    | √         |

#### 1Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 3.3    | 3v to 3.4v    | $\checkmark$ |

| Ch2 | 3.3    | 3v to 3.4v    | V            |

| Ch3 | 3.3    | 3v to 3.4v    | V            |

| Ch4 | 3.3    | 3v to 3.4v    | <b>√</b>     |

#### 10Hz

|     | Output | Specification | Pass/Fail    |

|-----|--------|---------------|--------------|

| Ch1 | 0.48   | 0.4v to 0.5v  | $\checkmark$ |

| Ch2 | 0.48   | 0.4v to 0.5v  |              |

| Ch3 | 0.48   | 0.4v to 0.5v  |              |

| Ch4 | 0.46   | 0.4v to 0.5v  |              |

#### 100Hz

|     | Output | Specification  | Pass/Fail |

|-----|--------|----------------|-----------|

| Ch1 | 0.16   | 0.15v to 0.16v | V         |

| Ch2 | 0.16   | 0.15v to 0.16v | <b>√</b>  |

| Ch3 | 0.16   | 0.15v to 0.16v | <b>√</b>  |

| Ch4 | 0.16   | 0.15v to 0.16v | V         |

#### 1 KHz

|     | Output | Specification  | Pass/Fail |

|-----|--------|----------------|-----------|

| Ch1 | 0.16   | 0.14v to 0.16v | V         |

| Ch2 | 0.16   | 0.14v to 0.16v | V         |

| Ch3 | 0.16   | 0.14v to 0.16v | V         |

| Ch4 | 0.16   | 0.14v to 0.16v | <b>√</b>  |

| Unit        | OMC_3    | Serial No |

|-------------|----------|-----------|

| Test Engine | erXen    |           |

| Date        | 27/10/10 |           |

#### 9. Monitor Outputs

Remove links W4 and W5.

Connect a 39 ohm dummy load to each channel.

Apply a 1V r.m.s input at 10Hz measured between TP10 and TP14, and record the differential output from each monitor pair on P1 for each channel. Compare them with the voltage outputs (TP9 to TP13).

#### **Voltage monitors**

| Ch. | Nominal | Output<br>between<br>TP9 & TP13 | Monitor Pins<br>on P1 | Monitor<br>Voltage | Pass/Fail:<br>Equal?<br>(+/- 0.1v) |

|-----|---------|---------------------------------|-----------------------|--------------------|------------------------------------|

| 1   | 1.22V   | 1.22                            | Pin 1 to Pin 2        | 1.22               | $\checkmark$                       |

| 2   | 1.22V   | 1.22                            | Pin 5 to Pin 6        | 1.22               | $\checkmark$                       |

| 3   | 1.22V   | 1.22                            | Pin 9 to Pin 10       | 1.22               | $\sqrt{}$                          |

| 4   | 1.22V   | 1.22                            | Pin 13 to Pin 14      | 1.22               | V                                  |

#### **Current monitors**

| Ch. | Nominal | Monitor Pins     | Monitor O/P | Pass/Fail:<br>Equal?<br>(+/- 0.1v) |

|-----|---------|------------------|-------------|------------------------------------|

| 1   | V80.0   | Pin 3 to Pin 4   | 0.08        |                                    |

| 2   | 0.08V   | Pin 7 to Pin 8   | 0.08        | √                                  |

| 3   | 0.08V   | Pin 11 to Pin 12 | 0.08        | $\sqrt{}$                          |

| 4   | 0.08V   | Pin 15 to Pin 16 | 0.08        |                                    |

#### 10. Distortion

Filter out. Increase input voltage to 10v peak, f = 1KHz. Dummy 39 Ohm loads. Observe the voltage across each load with an oscilloscope.

|     | Distortion Free? |  |

|-----|------------------|--|

| Ch1 | $\sqrt{}$        |  |

| Ch2 | $\sqrt{}$        |  |

| Ch3 | $\sqrt{}$        |  |

| Ch4 | $\sqrt{}$        |  |

| Unit | OMC 3    | Serial No |

|------|----------|-----------|

|      |          |           |

| •    | 27/10/10 |           |

#### 11. DC Stability

Use the precision voltage source via a break out box on the input (J3). All filters off. Record the differential output voltage between TP7 and TP11. Check stability while slowly increasing the output voltage. (Link W2 in)

|      | J3 pins 1,6 |                    | J3 pins 2,7 |                    | J3 pins 3,8 |                    | J3 pins 4,9 |                    |

|------|-------------|--------------------|-------------|--------------------|-------------|--------------------|-------------|--------------------|

|      | Ch1<br>o/p  | Ch1<br>stable<br>? | Ch2<br>o/p  | Ch2<br>stable<br>? | Ch3 o/p     | Ch3<br>stable<br>? | Ch4<br>o/p  | Ch4<br>stable<br>? |

| -10v | -24.5       | V                  | -24.5       | V                  | -24.5       | <b>V</b>           | -24.5       |                    |

| -7v  | -17.4       | <b>V</b>           | -17.3       | <b>V</b>           | -17.3       | <b>V</b>           | -17.4       | <b>√</b>           |

| -5v  | -12.5       | V                  | -12.5       | V                  | -12.4       | <b>V</b>           | -12.5       |                    |

| -1v  | -2.5        | V                  | -2.4        |                    | -2.4        | <b>V</b>           | -2.4        | $\sqrt{}$          |

| 0v   | 0           | V                  | 0           | <b>√</b>           | 0           | $\sqrt{}$          | 0           |                    |

| 1v   | 2.4         | V                  | 2.5         | V                  | 2.4         | <b>V</b>           | 2.4         | V                  |

| 5v   | 12.1        | V                  | 12.5        | <b>√</b>           | 12.3        | <b>V</b>           | 12.0        | V                  |

| 7v   | 17.0        | V                  | 17.2        | <b>√</b>           | 17.0        | <b>V</b>           | 17.0        | V                  |

| 10v  | 24.5        | <b>1</b>           | 24.5        |                    | 24.5        | <b>√</b>           | 24.5        |                    |

| Unit          | Serial No |

|---------------|-----------|

| Test Engineer | •••       |

| Date          |           |

#### 12. Crosstalk Tests

The purpose of these tests is to determine the level of crosstalk between each of the channels. As this is a lengthy test, and is mainly a function of board layout, it may be decided to perform the full test on a sample board only, and repeat the quick test on subsequent units.

#### 12.1 Full Test

As crosstalk is a function of board layout, this test is only necessary on a sample basis.

Use the HP Dynamic signal analyser to measure the cross talk between adjacent channels.

Apply the source, set at 1v r.m.s, to each channel in turn, via the differential driver, while grounding the inputs to adjacent channels.

Measure the transfer function to adjacent channels.

Record the maximum outputs on adjacent channels, and record the frequency at which this occurs. (Assuming an output signal is detectable).

| INPUT<br>CHANNEL | OUTPUT<br>CHANNEL | Maximum<br>Output | @ Frequency |

|------------------|-------------------|-------------------|-------------|

| Channel 1        | Channel 2         |                   |             |

| Channel 2        | Channel 1         |                   |             |

| Channel 2        | Channel 3         |                   |             |

| Channel 3        | Channel 2         |                   |             |

| Channel 3        | Channel 4         |                   |             |

| Channel 4        | Channel 3         |                   |             |

| Unit | OMC 3.   | Serial No |

|------|----------|-----------|

|      |          |           |

| _    | 27/10/10 |           |

#### 13. Dynamic Range Tests

In this test, the board is tested at maximum dynamic range.

Connect a 39 Ohm load resistor to the output of each channel. Switch out the filters. Apply a 10v peak sinusoidal signal at 10 Hz to the input. Check that the signal on TP10 is 10v peak.

Observe the differential output voltage across the load resistors with an oscilloscope. Check that the waveforms are not clipping.

|           | Ch1       | Ch2       | Ch3       | Ch4          |

|-----------|-----------|-----------|-----------|--------------|

| Not       | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | $\checkmark$ |

| Clipping? |           |           |           |              |

|     | Theoretical o/p | Measured | OK+/- 0.1v?  |

|-----|-----------------|----------|--------------|

| Ch1 | 1.12v           | 1.13     | $\sqrt{}$    |

| Ch2 | 1.12v           | 1.13     | $\sqrt{}$    |

| Ch3 | 1.12v           | 1.13     | $\checkmark$ |

| Ch4 | 1.12v           | 1.13     | $\checkmark$ |

# LIGO Laboratory / LIGO Scientific Collaboration

# LIGO-T1000567-v1 Advanced LIGO UK

29 September 2010

**OMC Coil Driver Board Test Plan**

R. M. Cutler, University of Birmingham

Distribution of this document: Inform aligo\_sus

This is an internal working note of the Advanced LIGO Project, prepared by members of the UK team.

#### **Institute for Gravitational Research University of Glasgow**

Phone +44 (0) 141 330 5884 Fax +44 (0) 141 330 6833

E-mail <u>k.strain@physics.gla.ac.uk</u> **Engineering Department**

**CCLRC Rutherford Appleton Laboratory** Phone +44 (0) 1235 445 297

Fax +44 (0) 1235 445 843 E-mail <u>J.Greenhalgh@rl.ac.uk</u>

# School of Physics and Astronomy University of Birmingham

Phone +44 (0) 121 414 6447

Fax +44 (0) 121 414 3722

E-mail av@star.sr.bham.ac.uk **Department of Physics**

**Department of Physics University of Strathclyde**Phone +44 (0) 1411 548 3360

Fax +44 (0) 141 552 2891

E-mail N.Lockerbie@phys.strath.ac.uk

http://www.ligo.caltech.edu/

http://www.physics.gla.ac.uk/igr/sus/

http://www.sr.bham.ac.uk/research/gravity/rh,d,2.html

http://www.eng-external.rl.ac.uk/advligo/papers\_public/ALUK\_Homepage.htm

# OMC COIL DRIVER BOARD TEST PLAN

| Unit | OMC_4    | Serial No |  |

|------|----------|-----------|--|

|      |          |           |  |

| Date | 27/10/10 | 0         |  |

#### **Contents**

- 1. Description

- 2. Test Equipment

- 3. Inspection

- 4. Continuity Checks

- 5. Test Set Up

- 6. Power

- 7. Relay operation

- 8. Corner Frequency Tests

- 9. Monitor Outputs

- 10. Distortion

- 11. DC Stability

- 12. Crosstalk Tests

- 13. Dynamic range

#### 1. Description

#### **Block diagram**

#### 2. Description

Each OMC Driver board consists of four identical channels and three power regulators, which provide regulated power to the four channels.

Taking the diagram block by block, the first block contains relays which switch the circuit between the normal inputs and the test inputs.

The second block contains a low pass filter with a corner frequency of 1 Hz, followed by a complimentary zero at 10 Hz. To a good approximation, the gain is reduced by a factor of 0.7 at 1 Hz, the attenuation increases at a rate of 20dB/decade up to the corner frequency of the zero at 10 Hz, after which the characteristic levels off. This filter may be switched in and out as required by relay control. Operational amplifiers follow which have a gain of 1.2.

The third block contains a filter with a similar characteristic, the main difference being that this filter is not switchable.

This is followed by the output buffer stage, consisting of an operational amplifier followed by a power driver buffer. The power driver is unity gain, and the operational amplifier provides the gain in this stage. The loop is closed around the buffer/operational amplifier pair. The current limit is set to 0.25A.

The outputs are buffered by unity gain voltage followers which drive the monitor board.

| Unit | OMC 4   | 4Serial No |

|------|---------|------------|

|      |         |            |

| Date | 27/10/1 | 0          |

#### 2. Test equipment

Power supplies (At least +/- 20v variable, 1A)

Signal generator (capable of delivering 10v peak, 0.1Hz to 10 KHz))

Digital oscilloscope

Analogue oscilloscope

Agilent Dynamic Signal Analyser (or similar)

Low noise Balanced Driver circuit

Relay test box

Record the Models and serial numbers of the test equipment used below.

| Unit (e.g. DVM)    | Manufacturer     | Model   | Serial Number |

|--------------------|------------------|---------|---------------|

| Signal Generator   | Agilent          | 33250A  |               |

| Oscilloscope       | ISO-TECH         | ISR622  |               |

| PSU*2              | Farnell          | L30-2   |               |

| DVM                | Fluke            | 77111   |               |

| Signal analyzer    | Agilent          | 35670A  |               |

| Pre-amplifier      | Stanford Systems | SR560   |               |

| DVM                | TENMA            | 72-7730 |               |

| V/I calibrator     | Time Electronics | 1044    |               |

| Function Generator | Hitachi          | VG-4429 |               |

| Unit | OMC 4. | Serial No |

|------|--------|-----------|

|      |        |           |

| -    |        |           |

# 3. Inspection

#### Workmanship

Inspect the general workmanship standard and comment:  $\sqrt{\phantom{a}}$

C21 and C26 have been replaced by a 10nF polypropylene capacitor on all channels.

C200 has been soldered across R5 and R23 on all channels.

#### Links:

Check that links W4 and W5 are present on each channel. If not, connect them.

| Unit          | OMC 4    | Serial No |  |

|---------------|----------|-----------|--|

| Test Engineer | Xen      |           |  |

| Date          | 27/10/10 |           |  |

# 4. Continuity Checks

J2

| PIN    | SIGNAL | DESCRIPTION   | To J1 PIN | OK?       |

|--------|--------|---------------|-----------|-----------|

| 1      | PD1P   | Photodiode A+ | 1         | $\sqrt{}$ |

| 2      | PD2P   | Photodiode B+ | 2         | $\sqrt{}$ |

| 3      | PD3P   | Photodiode C+ | 3         | $\sqrt{}$ |

| 4      | PD4P   | Photodiode D+ | 4         |           |

| 5 0V √ |        |               |           |           |

| 6      | PD1N   | Photodiode A- | 14        | $\sqrt{}$ |

| 7      | PD2N   | Photodiode B- | 15        |           |

| 8      | PD3N   | Photodiode C- | 16        | $\sqrt{}$ |

| 9      | PD4N   | Photodiode D- | 17        |           |

**J5**

| PIN | SIGNAL |    | To J1 PIN | OK?      |

|-----|--------|----|-----------|----------|

| 1   | Imon1P |    | 5         | <b>√</b> |

| 2   | Imon2P |    | 6         | V        |

| 3   | Imon3P |    | 7         | V        |

| 4   | Imon4P |    | 8         | V        |

|     | 5      | 0V | V         |          |

| 6   | Imon1N |    | 18        | V        |

| 7   | Imon2N |    | 19        | V        |

| 8   | Imon3N |    | 20        | V        |

| 9   | Imon4N |    | 21        | V        |

# Power Supply to Satellite box J1

| PIN | SIGNAL   | DESCRIPTION | OK?      |

|-----|----------|-------------|----------|

| 9   | V+ (TP1) | +17v Supply |          |

| 10  | V+ (TP1) | +17v Supply | <b>√</b> |

| 11  | V- (TP2) | -17v Supply | <b>√</b> |

| 12  | V- (TP2) | -17v Supply | √        |

| 13  | 0V (TP3) |             | √        |

| 22  | 0V (TP3) |             | <b>√</b> |

| 23  | 0V (TP3) |             | <b>√</b> |

| 24  | 0V (TP3) |             | √        |

| 25  | 0V (TP3) |             | √        |

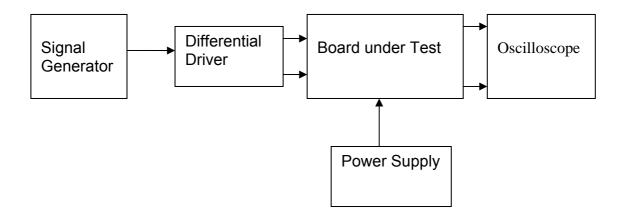

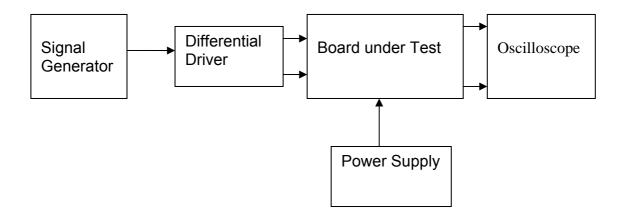

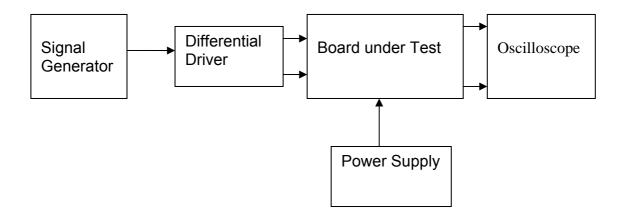

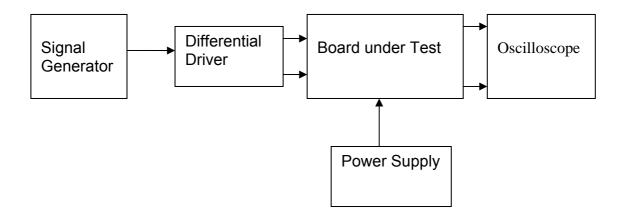

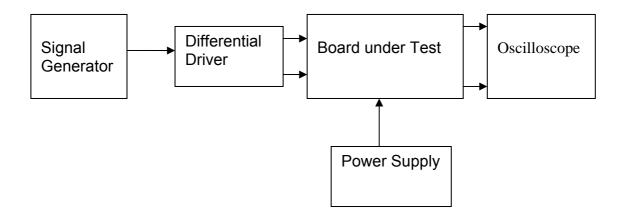

#### 5. TEST SET UP

#### Note:

- (1) Input signal to differential amplifier is generally stated in the tests below. There is therefore an inherent gain of 2 in the system.

- (2) Some signal generators will indicate 1vpk/pk when the output is in fact 1v Peak into the high impedance Differential driver used. The test procedure refers to the actual voltage out of the signal generator.

#### **Connections:**

Differential signal inputs to the board under test:

J3 pins 1, 2,  $\overline{3}$ , 4 = positive input

J3 pins 6, 7, 8, 9 = negative input

J3 pin 5 = ground

#### Power

J1 pin 9, 10 = +16.5v

J1 pin 11,12 = -16.5

J1 pins 22, 23, 24, 25 = 0v

#### Outputs

| Ch1- = J4 pin 9  |

|------------------|

| Ch2- = J4 pin 11 |

| Ch3- = J4 pin 13 |

| Ch4- = J4 pin 15 |

|                  |

| Unit | OMC_4    | Serial No |  |

|------|----------|-----------|--|

|      | Xen      |           |  |

| Date | 27/10/10 |           |  |

#### 6. Power

# Check the polarity of the wiring:

#### 3 Pin Power Connector

Set the power supply outputs to zero.

Connect power to the unit

Increase the voltages on the supplies to +/-3V.

Determine that the supply polarities are correct on TP1 and TP2.

If they are, increase input voltages to +/- 16.5v.

Record the output voltages, measured on a 4 digit DVM, from each regulator Observe the output on an analogue oscilloscope, set to AC. Measure and record the peak to peak noise on each output.

Record regulator outputs:

| Regulator | Output voltage | Output noise | Nominal<br>+/- 0.5v? |

|-----------|----------------|--------------|----------------------|

| +12v TP5  | 11.98          | 1mV          | √                    |

| +15v TP4  | 14.93          | 1mV          | √                    |

| -15v TP6  | -15.03         | 5mV          | <b>√</b>             |

| All Outputs smooth DC, no oscillation? | 1 |  |

|----------------------------------------|---|--|

|----------------------------------------|---|--|

Record Power Supply Currents

| Supply | Current |

|--------|---------|

| +16.5v | 350mA   |

| -16.5v | 250mA   |

If the supplies are correct, proceed to the next test.

| Unit | OMC_4    | Serial No |  |

|------|----------|-----------|--|

|      | Xen      |           |  |

| Date | 27/10/10 |           |  |

# 7. Relay Operation

Operate each relay in turn.

Observe its operation. LEDs should illuminate when the relays are operated.

#### **Filter**

| Channel | Indi | Indicator |   |

|---------|------|-----------|---|

|         | ON   | OFF       |   |

| Ch1     | V    |           | V |

| Ch2     | V    |           | V |

| Ch3     | V    |           |   |

| Ch4     |      |           |   |

#### **Test Switches**

| Channel | Indi     | Indicator |   |

|---------|----------|-----------|---|

|         | ON       | OFF       |   |

| Ch1     | V        |           | V |

| Ch2     | V        |           | V |

| Ch3     | V        |           | V |

| Ch4     | <b>√</b> |           |   |

| Unit          | OMC_4    | Serial No |  |

|---------------|----------|-----------|--|

| Test Engineer | Xen      |           |  |