### LASER INTERFEROMETER GRAVITATIONAL WAVE OBSERVATORY - LIGO -CALIFORNIA INSTITUTE OF TECHNOLOGY MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Technical Note

LIGO-T060212-00 - D

9/6/06

# **CONVERTER UPLINK**

Paul Schwinberg, Josh Myers, Daniel Sigg

Distribution of this draft:

all

This is an internal working note of the LIGO Project.

LIGO Hanford Observatory P.O. Box 159 Richland, WA 99352 Phone (509) 372-8106 FAX (509) 372-8137 E-mail: info@ligo.caltech.edu

#### California Institute of Technology LIGO Project - MS 51-33 Pasadena CA 91125 Phone (626) 395-2129 Fax (626) 304-9834 E-mail: info@ligo.caltech.edu

LIGO Livingston Observatory 19100 LIGO Lane Livingston, LA 70754 Phone (504) 686-3100 FAX (504) 686-7189 E-mail: info@ligo.caltech.edu

Massachusetts Institute of Technology LIGO Project - MS NW17-161 Cambridge, MA 01239 Phone (617) 253-4824 Fax (617) 253-7014 E-mail: info@ligo.mit.edu

# **Table of Contents**

| <b>1</b> INT   | RODUCTION AND OVERVIEW           | 3  |

|----------------|----------------------------------|----|

| 2 TIN          | ING AND CLOCK SIGNALS            | 4  |

| 3 UP           | LINK BLOCK DIAGRAM               | 6  |

| 3.1 T          | RANSMIT ENGINE                   | 7  |

| 3.1.1          | Transmit Arbiter                 |    |

| 3.1.2          | Transmit Microcode State Machine |    |

|                | Low Priority Transmit Queue      |    |

|                |                                  |    |

| 3.2.1          | Receive Arbiter                  |    |

| 3.2.2<br>3.2.3 | Receive Microcode State Machine  |    |

|                | Low Priority Receive Queue       |    |

| 3.3.1          | IO Space                         |    |

| 3.3.2          | Memory Space                     |    |

|                |                                  |    |

| 4 ET           | HERNET PROTOCOL2                 | .6 |

| 4.1 P          | ROTOCOL SUBTYPES                 |    |

| 4.1.1          | Configuration Frame              |    |

| 4.1.2          | Converter Data Frame             | 28 |

| 5 To           | OLS2                             | .9 |

| 5.1 C          | ONFIGURATION SETUP               | 29 |

| 5.1.1          | Mnemonic                         | 29 |

| 5.1.2          | confasm                          | 29 |

| 5.1.3          | confprom                         | 30 |

# **1** INTRODUCTION AND OVERVIEW

This note describes the uplink interface of the converter units. The interface consists of 2 physical gigabit ethernet ports. SFP fiber transceivers are used and can therefore support either single mode or multi mode fibers. Both physical interfaces can be used independently. For example, one could be dedicated for a servo control system whereas the other one could be used by a data acquisition system.

The protocol is based on a basic ethernet frame without any IP extensions. This should allow for simple and low latency interface on the computer end. Each interface has to be programmed through its port to select the converter channels and to select the acquisition rate.

The converter unit operates at a fixed sampling rate of  $2^{19}$  Hz (524.288kHz). An optional decimation filter is available for each channel. The user programmed acquisition rate must be an integer fraction of the sampling rate and not lower than 1 Hz. It is also possible to define a processing rate which is slower than the acquisition rate. This will then lead to multiple data samples per converter transferred by each ethernet frame.

Since all channels of one acquisition cycle have to be copied to the ethernet frame within one sampling period, a maximum number of about 100 channels can be transferred at once. It is however possible to increase this number by shifting the start of the acquisition cycle for some channels by an integral of the sampling period. The uplink supports jumbo ethernet frames up to 9000 bytes long. In reality however, the number of channel data words which can be transferred by each processing cycle is limited by the on chip FIFO buffers. For both input and output channels the limit is about 1000 channels per FIFO.

To allow for greater flexibility each gigabit ethernet interface supports up to 4 independent FIFO buffers or data queues in both directions. Each of this data queues can be programmed independently to support different data rates and to support interfacing multiple hosts. The only limitation is that the 4 queues access the converters one after the other. Meaning there is a transfer limit of 100 channels total per sampling period. However, each queue can easily be aligned to a different sampling period to avoid this problem.

The interface also supports binary input and output. A binary input will be treated just like a 32 bit analog-to-digital value, whereas a binary output will be treated like a 32 bit digital-to-analog value. For this application the decimation filter can be bypassed.

Section 2 gives an overview of the timing convention. Section 3 goes into more details about the functioning of the uplink interface. And section 4 gives a detailed description of the used ethernet protocol.

# 2 TIMING AND CLOCK SIGNALS

The following timing and clock signals are used by the converter board:

- *i)* Master clock at  $2^{26}$  Hz (67.108864 MHz). This clock is locked to the  $2^{23}$  Hz (8.388608 MHz) clock from the timing distribution.

- *ii)* 1PPS (one pulse per second). The 1PPS is synchronized with the GPS clock and also derived from the timing distribution system.

- *iii)* The sampling clock. This is the conversion rate of the ADCs and DACs. For a low noise ADC such as the AD7679 this clock runs at 2<sup>19</sup> Hz (524.288kHz) and is derived from the master clock and synchronized by the 1PPS.

- *iv*) The acquisition clock. This is the rate the data is acquired and is typically a decimated version of the sampling clock. Most often its rate is  $2^{14}$  Hz (16.384kHz). This clock is aligned with the sampling clock but its rising edge can be shifted relative to the 1PPS. With the typical rates above there are  $32 (2^{19}/2^{14})$  possibilities to align the acquisition clock to the sampling clock. Basically, this allows the acquisition clock to be adjusted in small increments within a processing cycle.

- v) The processing clock. This is the rate the data processing is clocked back on the computer side. It is also a power of two in frequency. It is also the rate the data is shipped through the uplink interface. In most circumstances its rate is the same as the acquisition rate. However, it is always aligned to the 1 PPS. If the acquisition rate is higher than the processing rate multiple data consecutive converter words are shipped per uplink request.

- *vi*) The uplink clock. This is the clock of the uplink interface. For gigabit ethernet and 16bit words this rate is 62.5 MHz, or about 7% lower than the master clock. It is not aligned with the 1PPS.

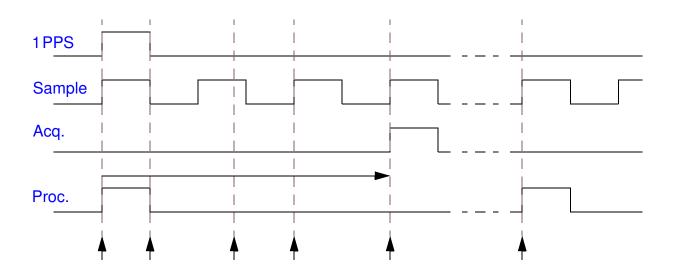

In Figure 1 an example of a timing diagram is shown. At time the sample clock and the processing clock are aligned to the 1PPS. The period of the sampling clock is about  $2 \mu$ s and the ). There are 32 sampling clock periods ( ) period of the processing clock is about  $61 \,\mu\,s$  (to for every processing clock. In this example the ADC conversion clock is applied at time in the middle of a sampling period. The ADC then requires somewhat less than  $2\mu$ s to complete the ). The ADC is then read through the serial interface and the data is conversion (until about available in the FPGA at time and . The time between is used by the decimation filter. This sampling process is repeated at the sampling rate using a pipeline. The acquisition clock is at the same rate as the processing clock but in this example delayed by 3 clock cycles . Data will be ready for sending through the uplink interface at time . Converter data which has passed through the decimation filter and which is ready at each sampling period is ignored in between the acquisition clock—or in other words in this example only every 32<sup>nd</sup> converter word is read out.

The sampling clock is typically fixed and depends on the exact converter chips which is used. However, the user can specify both the acquisition rate and the processing rate as well as the offset of the acquisition clock relative to the processing clock (in increments of the sampling period). Obviously, the ratio between the acquisition rate and the sampling rate determines the corner frequency of the decimation filter.

Figure 1: Timing diagram example.

# **3 UPLINK BLOCK DIAGRAM**

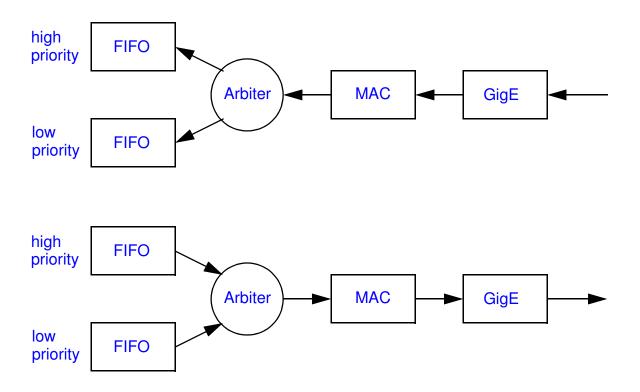

Figure 2 shows block diagrams of the receiver and transmitter sections of the uplink interface. Data is received through gigabit ethernet and forwarded to a ethernet MAC (Media Access Controller). This is part of the available resources of the selected FPGA. The gigabit ethernet interface is fiber based. After the MAC a priority arbiter decides whether the ethernet frame goes in the high priority FIFO (low latency) or the low priority FIFO. The high priority FIFO handles converter data (in this case DAC data) only, whereas the low priority FIFO handles all the other requests such as configuration commands and status information. The decision whether an ethernet frame is low or high priority is based on the protocol subtype.

The transmitter block diagram is essentially the same as the receiver one—just with the data flow arrows pointing the opposite way. The arbiter will always give priority to the high priority FIFO. Furthermore, it will only accept ethernet frames from the low priority FIFO in the middle of the acquisition cycle to prevent conflicts and make sure converter data is sent to the uplink interface without delay.

As a matter of fact both transmit and receive sections support up to 4 high priority queues. The idea is to be able to support multiple destinations for the sampled data. For example, there can be one data queue dedicated for the servo control system and another one for the data acquisition system. Furthermore, it allows to support multiple data rates simultaneously. A diagnostics system may request data at full rate while a servo control system is running. Conversely, on the receiving side multiple converters can be fed from different processing systems. A converter unit

Figure 2: Block diagram of receiver and transmitter link interface.

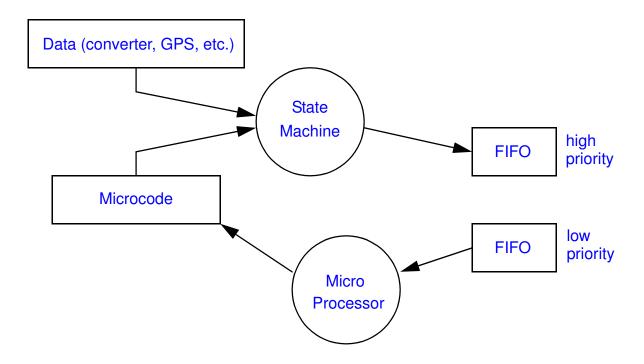

#### Figure 3: Block diagram of the transmitter state machine.

can also support more than a single physical uplink interface. This allows to keep data path from different systems—such as data acquisition and servo control system—completely separated.

Figure 3 shows the transmitter state machine which writes to the transmitter FIFOs, respectively. The FIFOs also mark the clock boundary between the uplink clock and the converter clocks. On the MAC side 16bit words are processed at a rate of 62.5 MHz, whereas on the state machine side they get processed at a rate of 67.108864 MHz. The state machine is programmable by microcode which is stored in a dual ported RAM. It is triggered every time an acquisition cycle starts.

The receiver state machine is similar to the transmitter one but with the data flow going the opposite direction. The state machine is triggered every time a frame is received.

# **3.1 TRANSMIT ENGINE**

The transmit engine consists of 5 transmission queues: A through D and LP (low priority). The FIFOs associated with queues A through D are fed by the microcode state machine, whereas the LP FIFO is fed by the microprocessor and handles lower priority configuration and status requests.

### 3.1.1 Transmit Arbiter

The transmitter FIFOs are 17 bits wide. 16 bits are copied to the ethernet MAC as data whereas the 17th bit serves to mark the end of frame. Each FIFO also has a 'go' bit which is used to start the ethernet frame transmission. Up to 16 'go' commands can be stacked up and therefore up to 16 ethernet frames can be backed up in a FIFO—assuming there is enough storage space. The

#### LIGO-T060212-00

transmit arbiter also provides a status word which indicates an overflow or underflow in each of the FIFOs as well as an error in one of the 'go' command bits. If multiple frames are ready at the same time the arbiter will first empty the FIFO of queue A, then move to B, C, D and finally LP. Furthermore, the LP queue is only served in between data transmissions. This window can be set by the management processor, see Table 1.

| Configuration Word | Offset | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPStart            | 0x0030 | R/W    | This word indicates the beginning of the low priority queue window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LPStop             | 0x0034 | R/W    | This word indicates the end of the low priority queue window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LPMask             | 0x0038 | R/W    | This word indicates the mask which is used to determine the window alignment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TransmitStatus     | 0x003C | R      | The lower 16 bits represent the status of the transmit<br>arbiter. (Writing to this address will send data to the<br>EMAC!)<br>Bit 0 (LSB): FIFO A overflow<br>Bit 1: FIFO A underflow<br>Bit 2: FIFO A too many 'go' commands<br>Bit 3: FIFO B overflow<br>Bit 4: FIFO B underflow<br>Bit 5: FIFO B too many 'go' commands<br>Bit 6: FIFO C overflow<br>Bit 7: FIFO C underflow<br>Bit 8: FIFO C too many 'go' commands<br>Bit 9: FIFO D overflow<br>Bit 10: FIFO D underflow<br>Bit 11: FIFO D too many 'go' commands<br>Bit 12: FIFO LP overflow<br>Bit 13: FIFO LP underflow<br>Bit 14: FIFO LP too many 'go' commands<br>Bit 15: arbiter transmit error |

#### Table 1: Arbiter configuration in the transmit IO space.

The valid transmit window of the LP queue is computed as follows:

$LP_{valid} = (cnt \land LPmask > LPStart \land LPmask) \land (cnt \land LPmask \le LPStop \land LPmask)$ (1)

where cnt is a counter value derived from the 67.108864MHz clock and synchronized with the 1PPS from the timing system. It counts from 0 to 67108863 every second.

Example: If the frame transmit rate is 16384Hz, the LPMask has to be 0x00000FFF. Meaning only 12 bits of the counter are used and thus it repeats every  $61 \,\mu$  s. The LPStart and the LPStop values could then be set to 0x00000800 and 0x00000A00, respectively. This would allow for the transmission of low priority ethernet frames from  $30.5 \,\mu$  s to  $38.2 \,\mu$  s into the cycle. A valid mask must always be filled with ones from the right.

# 3.1.2 Transmit Microcode State Machine

#### 3.1.2.1 **Programming the Acquisition Rate**

The transmit microcode state machine consists of 4 microcode tables which are associated with transmission queues A through D. The start of each microcode state machine is programmed through the IO configuration space of the management processor. Table 2 lists the configuration words.

| Configuration Word | Offset | Access | Description                                                                                                                                                                                    |

|--------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATRIG              | 0x0000 | R/W    | This word indicates the start condition for the microcode state machine A. Bit 0 is used as an enable for the state machine.                                                                   |

| BTRIG              | 0x0004 | R/W    | This word indicates the start condition for the microcode state machine B. Bit 0 is used as an enable for the state machine.                                                                   |

| CTRIG              | 0x0008 | R/W    | This word indicates the start condition for the microcode state machine C. Bit 0 is used as an enable for the state machine.                                                                   |

| DTRIG              | 0x000C | R/W    | This word indicates the start condition for the microcode state machine D. Bit 0 is used as an enable for the state machine.                                                                   |

| AMASK              | 0x0010 | R/W    | This word indicates the mask which is used to determine the length of the acquisition cycle of the microcode state machine A.                                                                  |

| BMASK              | 0x0014 | R/W    | This word indicates the mask which is used to determine the length of the acquisition cycle of the microcode state machine B.                                                                  |

| CMASK              | 0x0018 | R/W    | This word indicates the mask which is used to determine the length of the acquisition cycle of the microcode state machine C.                                                                  |

| DMASK              | 0x001C | R/W    | This word indicates the mask which is used to determine the length of the acquisition cycle of the microcode state machine D.                                                                  |

| AENDM              | 0x0020 | R/W    | This word indicates the mask which is used to<br>determine the length of the processing cycle as well as<br>mark the last acquisition in the processing cycle in<br>microcode state machine A. |

| BENDM              | 0x0024 | R/W    | This word indicates the mask which is used to<br>determine the length of the processing cycle as well as<br>mark the last acquisition in the processing cycle in<br>microcode state machine B. |

#### Table 2: Acquisition rate configuration in the transmit IO space.

| CENDM          | 0x0028 | R/W | This word indicates the mask which is used to<br>determine the length of the processing cycle as well as<br>mark the last acquisition in the processing cycle in<br>microcode state machine C. |

|----------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DENDM          | 0x002C | R/W | This word indicates the mask which is used to<br>determine the length of the processing cycle as well as<br>mark the last acquisition in the processing cycle in<br>microcode state machine D. |

| TransmitStatus | 0x003C | R   | The upper 16 bits represent the status of the transmit<br>microcode state machine. (Writing to this address will<br>send data to the EMAC!)<br>Bit 16: decoder error<br>Bit 17 to 31: not used |

### Table 2: Acquisition rate configuration in the transmit IO space.

Only the most significant 26 bits of the trigger and mask values are used. The most significant bit indicates the half second count, whereas the least significant bit (bit 6 in the 32 bit word) marks the clock count at  $2^{26}$  Hz. The last 6 bits should be set to one except bit 0 of the trigger value which is used as an enable.

The acquisition rate is determined by TRIG and MASK (interpreted as 26 bit values) using the following formula:

$$go = (cnt \land MASK = (TRIG + 1) \land MASK)$$

(2)

The cnt value is derived from a 26 bit counter which is synchronized with the 1PPS signal and is clocked at a rate of  $2^{26}$  Hz. A valid mask must always be filled with ones from the right. Also (TRIG + 1) has to be multiple of the sampling cycle. i.e., a multiple of 0x80. If the processing cycle is longer than the acquisition cycle, i.e., there are multiple samples acquired in each processing cycle, the ENDM mask has to be set accordingly

$$last = (cnt \wedge ENDM = (TRIG + 1) \wedge ENDM)$$

(3)

otherwise it should be set equal to MASK. The lowest supported acquisition and processing rate is 1 Hz.

Example 1: The processing cycle has a rate of 16.384kHz (or a period of 61  $\mu$  s) and we want to acquire 4 samples in each processing cycle. This means the acquisition cycle has a rate of 65.536kHz. This yields a MASK value of 0x0003FF and the ENDM value becomes 0x000FFF. The TRIG value can now be set to adjust the last sample in the processing cycle. If we choose to start the acquisition with the sample aligned to the 1PPS, the TRIG value should be set to 0x000BFF. The acquisition cycle that starts at 45.8  $\mu$  s is then marked as the last cycle, whereas the one which starts at 0  $\mu$  s is marked as the first. The ones which start at 15.3  $\mu$  s and 30.5  $\mu$  s will have no marking. Don't forget to insert 6 ones at the end of each value when setting the register values.

Example 2: Both the processing and the acquisition cycle are at a rate of 2048Hz. The MASK and ENDM values are then both set to 0x007FFF. The TRIG value is 0x007FFF and all acquisition cycles are marked as 'last'.

The most significant bit of the TRIG value is used to enable the microcode state machine. Therefore, it should be written after the MASK and ENDM values have been set. Also, in order to stop the acquisition process a zero should be written into the TRIG value first.

#### 3.1.2.2 **Programming the State Machine**

The 4 transmit states machines associated with queues A through D can be programmed through dual ported RAM. The transmit state machine uses an 32 bit wide decoder and a 32 bit wide data pool. Both of them are mapped into the memory space of the management processor. Table 3 describes the mapping.

| Memory block | Offset   | Access | Description                   |

|--------------|----------|--------|-------------------------------|

| A microcode  | 0x000000 | R/W    | Microcode of state machine A. |

| A data pool  | 0x002000 | R/W    | Data Pool of state machine A. |

| B microcode  | 0x004000 | R/W    | Microcode of state machine B. |

| B data pool  | 0x006000 | R/W    | Data Pool of state machine B. |

| C microcode  | 0x008000 | R/W    | Microcode of state machine C. |

| C data pool  | 0x00A000 | R/W    | Data Pool of state machine C. |

| D microcode  | 0x00C000 | R/W    | Microcode of state machine D. |

| D data pool  | 0x00E000 | R/W    | Data Pool of state machine D. |

#### Table 3: Mapping of the transmit state machine RAM into the processor memory space.

Each microcode pool contains 128 entries and each data pool contains 128 entries. Since the clock rate of the state machine is 67.108864MHz and the sampling rate is 524.288kHz, only the first ~125 entries are useful for storing code. Since state machines B, C and D run after A, the last command in state machine D should not be later than 125 clock cycles.

The microcode command structure is listed in Table 4.

#### Table 4: Transmitter microcode.

| Bit          | pipeline<br>delay | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|-------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 down to 0 | 2                 | Address | 12bits to address the data source. If the MSB is 0, the<br>remaining 11bits are used to address the ADC. If the MSB is<br>set, the address is used to decode the memory pool or the<br>GPS time stamp.<br>Memory map:<br>0x0000 to 0x07FF: ADC data<br>0x0800 to 0x087F: Memory pool<br>0x0A00: GPS time stamp (seconds)<br>0x0B00: GPS time stamp (fractional part)<br>0x0F00: all zeros. |

| 12           | —                 | _       | Not used at the moment.                                                                                                                                                                                                                                                                                                                                                                    |

| 15 down to 13 0 l       |              | Ignore on condition | Ignores the command depending on the condition of the first<br>and last flag of the acquisition process.<br>Bit 15: the acquisition cycles with the last flag set are ignored<br>Bit 14: the acquisition cycles in between set are ignored<br>Bit 13: the acquisition cycles with the first flag set are ignored |  |  |

|-------------------------|--------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 16                      | 0 FIFO write |                     | Write one 32 bit word into the FIFO                                                                                                                                                                                                                                                                              |  |  |

| 17 0 Start transmission |              | Start transmission  | Instructs the arbiter to start transmitting an ethernet frame.                                                                                                                                                                                                                                                   |  |  |

| 30 down to 18           | —            | —                   | Not used at the moment.                                                                                                                                                                                                                                                                                          |  |  |

| 31                      | 0            | End of program      | This indicates the last command in the microcode.                                                                                                                                                                                                                                                                |  |  |

### Table 4: Transmitter microcode.

It is important that the first instruction has the FIFO write and the start transmission flags set to zero. Otherwise, the FIFO will be filled and ethernet frames are scheduled for transmission with every clock cycle while state machine waits for the next 'go'. However, it is appropriate to load the first address. Because of the pipeline delay, it will only be available on the 3rd cycle anyway. Since the state machine can fill the FIFO faster than the arbiter can read it, it is also appropriate to give the start transmission command as one of the first instructions.

The state machine writes 32 bit words at a time to the EMAC FIFO. The first words must be the 32 most significant bits of the destination MAC address. The next word must be the remaining bits of the source address (mapped to the 16 most significant bits) as well as the 16 most significant bits of the source MAC address (mapped to the 16 least significant bits). The third word must be the remaining bits of the source MAC address. The forth word contains the frame type (mapped to the high bits) and the protocol subtype (mapped to the low bits). The fifth word contains the protocol version (mapped to the high bits) and the data length (mapped to the low bits).

Example: The destination MAC address is 00-13-20-04-4E-D1 and the source MAC address is DE-AD-FA-CE-00-01. The protocol subtype for the highest priority queue is then 80-00. Assuming we want to send 4 ADC data words the following words should be written to the A data pool (staring at zero offset): 0x00132004, 0x4ED1DEAD, 0xFACE0001, 0x88B58000, 0x00000018. To generate an ethernet frame these words should be sent to the EMAC FIFO in order followed by the GPS seconds, the GPS fractional seconds and the 4 ADC data words. For a more detailed description of the ethernet frame see section 4. The corresponding microcode is then 0x00000800, 0x00010801, 0x00010802, 0x00030803, 0x00010804, 0x00010A00, 0x00010B00, 0x00010000, 0x00010001, 0x00010002, 0x00010003, 0x00010F00, 0x80010F00. Keep in mind that there is a 2 cycle pipeline delay before the addressed data sample will be available for writing to the EMAC FIFO. Notice that the EMAC gets the start transmission command when the second data word is written to the FIFO.

### 3.1.2.3 Transmit Microcode Address Space

The address space of the state machine is 12 bits. The memory map is outlined below:

#### 3.1.2.4 Transmit Statistics Counter

Seven 32 bit statistics counters keep track of the number of errors in the transmit engine. These counters are clocked at a rate of  $2^{26}$  Hz. The counters are enabled by a low to high transition of

| Address         | Description                                             |  |

|-----------------|---------------------------------------------------------|--|

| 0x000           | ADC 1 filtered input                                    |  |

| 0x001           | ADC 2 filtered input                                    |  |

| 0x002           | ADC 3 filtered input                                    |  |

| 0x003           | ADC 4 filtered input                                    |  |

| 0x004           | ADC 1 input bypassing the filter                        |  |

| 0x005           | ADC 2 input bypassing the filter                        |  |

| 0x006           | ADC 3 input bypassing the filter                        |  |

| 0x007           | ADC 4 input bypassing the filter                        |  |

| 0x008 and 0x009 | ADC 2 minus ADC 1 filtered input                        |  |

| 0x00A and 0x00B | ADC 4 minus ADC 3 filtered input                        |  |

| 0x00C to 0x00F  | ADC 4 minus ADC 3 plus ADC 2 minus ADC 1 filtered input |  |

| 0x010 to 0x01F  | same as 0x000 to 0x00F but for ADCs 5 through 8         |  |

| 0x020 to 0x02F  | same as 0x000 to 0x00F but for ADCs 9 through 12        |  |

| 0x030 to 0x03F  | same as 0x000 to 0x00F but for ADCs 13 through 16       |  |

| 0x800 to 0x87F  | Memory pool                                             |  |

| 0xA00           | GPS time stamp (seconds)                                |  |

| 0xB00           | GPS time stamp (fractional part)                        |  |

| 0xF00           | all zeros                                               |  |

#### Table 5: Layout of the transmit microcode address space.

the corresponding bits in the transmit status word. The statistics counters are mapped into the transmit IO space and are listed in Table 6.

#### Table 6: Statistics counters in the transmit IO space.

| Configuration Word | Offset | Access | Description                                                                                                                                                        |

|--------------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AFIFO_ERR          | 0x0040 | R      | Counts the number of errors in the FIFO of the transmit<br>queue A. Any of the corresponding bits in the transmit<br>status going high will increase this counter. |

| BFIFO_ERR          | 0x0044 | R      | Counts the number of errors in the FIFO of the transmit<br>queue B. Any of the corresponding bits in the transmit<br>status going high will increase this counter. |

| CFIFO_ERR          | 0x0048 | R      | Counts the number of errors in the FIFO of the transmit<br>queue C. Any of the corresponding bits in the transmit<br>status going high will increase this counter. |

| DFIFO_ERR          | 0x004C | R      | Counts the number of errors in the FIFO of the transmit<br>queue D. Any of the corresponding bits in the transmit<br>status going high will increase this counter. |

| LPFIFO_ERR  | 0x0050 | R | Counts the number of errors in the FIFO of the transmit<br>low priority queue. Any of the corresponding bits in the<br>transmit status going high will increase this counter. |

|-------------|--------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARBITER_ERR | 0x0054 | R | Counts the number of errors in the transmit arbiter. The corresponding bit in the transmit status going high will increase this counter.                                      |

| DECODE_ERR  | 0x0058 | R | Counts the number of errors in the decoder of the microcode state machine. The corresponding bit in the transmit status going high will increase this counter.                |

#### Table 6: Statistics counters in the transmit IO space.

# 3.1.3 Low Priority Transmit Queue

The low priority transmit queue is programmed by the management processor. Configuration and status frames are written to address 0x003C in the transmit IO space. The ethernet frame has to be written 16 bits at a time using the least significant bits of a 32 bit word. The 17th bit is then used to indicate the last data in the frame. It will also trigger the transmission of the frame the next time the low priority queue reaches the transmit valid window and no higher priority queues are ready.

# **3.2 RECEIVE ENGINE**

The receive engine consists of 5 receiver queues: A through D and LP (low priority). The FIFOs associated with queues A through D are used by the microcode state machine, whereas the LP FIFO is used by the microprocessor and handles lower priority configuration and status requests.

### 3.2.1 Receive Arbiter

Compared to the transmit arbiter the receive arbiter has to decode part of the ethernet frame to decide if a valid frame was received. It has to decode the target queue and make sure the frame is long enough. It also has to check the GPS time stamp to make sure data is received on time. To facilitate the decision process the arbiter has a 14 word buffer which is used to delay the ethernet frame. This delay buffer is used for the LP queue only since only data words are sent to the high priority queues. Since it is important to make sure that data is received for each processing cycle, the arbiter maintains diagnostics counters which count the number of times frames arrive too late, to early or not at all. *The sender has to guarantee that there are never two ethernet frames sent to the same queue (A through D) with identical time stamp in the same processing cycle.*

Data has to arrive at the receive arbiter two sampling cycles ( $\sim 4 \mu s$ ) prior to the first acquisition (or output) cycle. Otherwise, the receive microcode state machine will not have enough time to copy the data to the converter outputs. This also means that the maximum acquisition rate is a fourth of the sampling clock, or 131072Hz. To avoid frames arriving out of synchronization the allowed window is exactly one processing cycle long. The GPS time stamp of an arriving frame has to be the time of the first output cycle of the following processing cycle—when the data is actually written to the converter outputs. All frames which arrive outside their time window will be rejected.

The receive arbiter and the receive microcode state machine share the following configuration words.

| Configuration Word | Offset | Access | Description                                                                                                                                                                     |

|--------------------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATRIG              | 0x0000 | R/W    | This word indicates the start condition for the receive queue A. Bit 0 is used as an enable for the state machine and the arbiter.                                              |

| BTRIG              | 0x0004 | R/W    | This word indicates the start condition for the receive queue B. Bit 0 is used as an enable for the state machine and the arbiter.                                              |

| CTRIG              | 0x0008 | R/W    | This word indicates the start condition for the receive queue C. Bit 0 is used as an enable for the state machine and the arbiter.                                              |

| DTRIG              | 0x000C | R/W    | This word indicates the start condition for the receive queue D. Bit 0 is used as an enable for the state machine and the arbiter.                                              |

| AMASK              | 0x0010 | R/W    | This word indicates the mask which is used to determine the length of the output cycle of the receive queue A.                                                                  |

| BMASK              | 0x0014 | R/W    | This word indicates the mask which is used to determine the length of the output cycle of the receive queue B.                                                                  |

| CMASK              | 0x0018 | R/W    | This word indicates the mask which is used to determine the length of the output cycle of the receive queue C.                                                                  |

| DMASK              | 0x001C | R/W    | This word indicates the mask which is used to determine the length of the output cycle of the receive queue D.                                                                  |

| AENDM              | 0x0020 | R/W    | This word indicates the mask which is used to<br>determine the length of the processing cycle as well as<br>mark the last output in the processing cycle in receive<br>queue A. |

| BENDM              | 0x0024 | R/W    | This word indicates the mask which is used to<br>determine the length of the processing cycle as well as<br>mark the last output in the processing cycle in receive<br>queue B. |

| CENDM              | 0x0028 | R/W    | This word indicates the mask which is used to determine the length of the processing cycle as well as mark the last output in the processing cycle in receive queue C.          |

| DENDM              | 0x002C | R/W    | This word indicates the mask which is used to<br>determine the length of the processing cycle as well as<br>mark the last output in the processing cycle in receive<br>queue D. |

| ALEN               | 0x0030 | R/W    | This word indicates the length of the data frame for receive queue A.                                                                                                           |

| BLEN               | 0x0034 | R/W    | This word indicates the length of the data frame for receive queue B.                                                                                                           |

| CLEN          | 0x0038 | R/W | This word indicates the length of the data frame for receive queue C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DLEN          | 0x003C | R/W | This word indicates the length of the data frame for receive queue D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ReceiveStatus | 0x00F8 | R   | The lower 16 bits represent the status of the receive<br>arbiter, whereas the upper 16 bits represent the status<br>of the receive microcode state machine.<br>Bit 0: Data ready in the LP FIFO queue<br>Bit 1: Out-of-sync frame received on queue A<br>Bit 2: Out-of-sync frame received on queue B<br>Bit 3: Out-of-sync frame received on queue C<br>Bit 4: Out-of-sync frame received on queue D<br>Bit 5: Frame type error<br>Bit 6: Frame length error<br>Bit 15: Decoder error<br>Bit 16: Receiver queue A empty at start of output cycle<br>Bit 17: Receiver queue C empty at start of output cycle<br>Bit 18: Receiver queue D empty at start of output cycle<br>Bit 19: Receiver queue D empty at start of output cycle |

| frame         | 0x00FC | R   | Read a low priority frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 7: Configuration in the receive IO space.

### 3.2.2 Receive Microcode State Machine

The receive microcode state machine is somewhat simpler than its transmit counter part, since some of the processing has already be done by the receive arbiter. All that is left to do is to copy the data from the queue into the converter output.

#### 3.2.2.1 Programming the Output Rate

The output rate is determined by TRIG and MASK using the following formula:

$$go = (cnt \land MASK = (TRIG + 1) \land MASK)$$

(4)

The convention is the same as for setting the acquisition rate in the transmit microcode machine. A valid mask must always be filled with ones from the right and 6 ones have to be filled in from the right to form a 32 bit word. If the processing cycle is longer than the output cycle, i.e., there are multiple samples acquired in each processing cycle, the ENDM mask has to be set accordingly

$$last = (cnt \land ENDM = (TRIG + 1) \land ENDM)$$

(5)

otherwise it should be set equal to MASK. The start of the microcode state machine and the start of the arbiter receive window are then  $1.91 \,\mu$  s and  $4.29 \,\mu$  s ahead of the first output cycle in each processing cycle, respectively.

Example: The output rate is 16384Hz and aligned in the center of the 61  $\mu$ s processing cycle. The MASK and ENDM values would then both be set to 0x0003FFFF, and the TRIG value would be set to 0x0003FFFF.

#### 3.2.2.2 Programming the State Machine

The 4 receive states machines associated with queues A through D can be programmed through dual ported RAM. The transmit state machine uses a 32 bit wide decoder which is mapped into the memory space of the management processor. Table 8 describes the mapping.

| Memory block | Offset   | Access | Description                   |

|--------------|----------|--------|-------------------------------|

| A microcode  | 0x000000 | R/W    | Microcode of state machine A. |

| B microcode  | 0x004000 | R/W    | Microcode of state machine B. |

| C microcode  | 0x008000 | R/W    | Microcode of state machine C. |

| D microcode  | 0x00C000 | R/W    | Microcode of state machine D. |

Table 8: Mapping of the receive microcode RAM into the processor memory space.

Each microcode pool contains 128 entries. Since the clock rate of the state machine is 67.108864MHz and the intrinsic output rate of the converters is 524.288kHz, all entries are useful for storing code. Since state machines B, C and D run after A, the last command in state machine D should not be later than 128 clock cycles.

The microcode command structure is listed in Table 9.

| Bit           | pipeline<br>delay | Name                | Description                                                                                                                                                                                                                                                                                     |

|---------------|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 down to 0  | 2                 | Address             | 12 bits to address the data source. If the MSB is 0, the<br>remaining 11 bits are used to address the DAC. If the MSB is<br>set, the address is ignored.<br>Memory map:<br>0x0000 to 0x07FF: DAC output data<br>0x0800 to 0x0FFF: not used                                                      |

| 12            | —                 | —                   | Not used at the moment.                                                                                                                                                                                                                                                                         |

| 15 down to 13 | 0                 | Ignore on condition | Ignores the command depending on the condition of the first<br>and last flag of the output process.<br>Bit 15: the outputs cycles with the last flag set are ignored<br>Bit 14: the outputs cycles in between set are ignored<br>Bit 13: the outputs cycles with the first flag set are ignored |

| 16            | 0                 | DAC write           | Reads one 32 bit word from the FIFO and writes it to the DAC output.                                                                                                                                                                                                                            |

| 30 down to 17 | —                 | —                   | Not used at the moment.                                                                                                                                                                                                                                                                         |

| 31            | 0                 | End of program      | This indicates the last command in the microcode.                                                                                                                                                                                                                                               |

#### Table 9: Receiver microcode.

There is pipeline delay for transferring data form the FIFO to a DAC output. The FIFO only contains data and the ethernet frame has been stripped.

#### 3.2.2.3 Receive Microcode Address Space

The address space of the state machine is 12 bits. The memory map is outlined below:

| Address        | Description                                                                        |  |

|----------------|------------------------------------------------------------------------------------|--|

| 0x000          | DAC 1 output with filter                                                           |  |

| 0x001          | DAC 2 output with filter                                                           |  |

| 0x002          | DAC 3 output with filter                                                           |  |

| 0x003          | DAC 4 output with filter                                                           |  |

| 0x004          | DAC 1 output bypassing the filter                                                  |  |

| 0x005          | DAC 2 output bypassing the filter                                                  |  |

| 0x006          | DAC 3 output bypassing the filter                                                  |  |

| 0x007          | DAC 4 output bypassing the filter                                                  |  |

| 0x008 or 0x009 | DAC 2 output with filter and negative DAC 1 output with filter                     |  |

| 0x00A or 0x00B | DAC 4 output with filter and negative DAC 3 output with filter                     |  |

| 0x00C to 0x00F | DAC 4 and DAC 2 output with filter and negative DAC 3 and DAC 1 output with filter |  |

| 0x010 to 0x01F | same as 0x000 to 0x00F but for DACs 5 through 8                                    |  |

| 0x020 to 0x02F | same as 0x000 to 0x00F but for DACs 9 through 12                                   |  |

| 0x030 to 0x03F | same as 0x000 to 0x00F but for DACs 13 through 16                                  |  |

#### Table 10: Layout of the receive microcode address space.

#### 3.2.2.4 Receive Statistics Counter

A number of 32 bit statistics counters keep track of the number of errors in the receive engine. These counters are clocked at a rate of  $2^{26}$  Hz. The counters are enabled by a low to high transition of the corresponding bits in the receive status word. The statistics counters are mapped into the receive IO space and are listed in Table 11.

| Configuration Word | Offset | Access | Description                                                                                                                                                                                        |

|--------------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_DISCARD          | 0x0040 | R      | Counts the number of discarded frames in receiver<br>queue A which were received outside the time window.<br>The corresponding bit in the receive status going high<br>will increase this counter. |

| B_DISCARD          | 0x0044 | R      | Counts the number of discarded frames in receiver<br>queue B which were received outside the time window.<br>The corresponding bit in the receive status going high<br>will increase this counter. |

| C_DISCARD          | 0x0048 | R      | Counts the number of discarded frames in receiver<br>queue C which were received outside the time window.<br>The corresponding bit in the receive status going high<br>will increase this counter. |

| D_DISCARD          | 0x004C | R      | Counts the number of discarded frames in receiver<br>queue D which were received outside the time window.<br>The corresponding bit in the receive status going high<br>will increase this counter. |

#### Table 11: Statistics counters in the receive IO space.

| A_MISSING  | 0x0050 | R | Counts the processing cycles on receiver queue A<br>which have not received a data frame in time. The<br>corresponding bit in the receive status going high will<br>increase this counter. |

|------------|--------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B_MISSING  | 0x0054 | R | Counts the processing cycles on receiver queue B<br>which have not received a data frame in time. The<br>corresponding bit in the receive status going high will<br>increase this counter. |

| C_MISSING  | 0x0058 | R | Counts the processing cycles on receiver queue C<br>which have not received a data frame in time. The<br>corresponding bit in the receive status going high will<br>increase this counter. |

| D_MISSING  | 0x005C | R | Counts the processing cycles on receiver queue D<br>which have not received a data frame in time. The<br>corresponding bit in the receive status going high will<br>increase this counter. |

| FTYPE_ERR  | 0x0060 | R | Counts frames with incorrect frame type or data frames<br>with incorrect protocol version. The corresponding bit in<br>the receive status going high will increase this counter.           |

| FLEN_ERR   | 0x0064 | R | Counts data frames with incorrect length. The corresponding bit in the receive status going high will increase this counter.                                                               |

| DECODE_ERR | 0x0068 | R | Counts the number of errors in the decoder of the microcode state machine. The corresponding bit in the receive status going high will increase this counter.                              |

#### Table 11: Statistics counters in the receive IO space.

# 3.2.3 Low Priority Receive Queue

The low priority receive queue is handled by the management processor. Configuration and status frames are read from address 0x00FC in the receive IO space. The full ethernet frame is available and has to be read 16 bits at a time using the least significant bits of the 32 bit word. The 17th bit is then used to indicate the last data in the frame. The receive status register at 0x00F8 indicates with bit 0, if a frame is available in the FIFO.

# **3.3 MANAGEMENT PROCESSOR**

A management processor is responsible to configure the transmit and receive engines as well as the ethernet MAC. It also handles the low priority queues and processes non-data ethernet frames.

# 3.3.1 IO Space

| IO block | Offset   | Description                                   |  |

|----------|----------|-----------------------------------------------|--|

| IOCFG0   | 0×000000 | Basic configuration                           |  |

| IOCFG1   | 0×080000 | Extended configuration                        |  |

| IOCLK    | 0x100000 | Interface to timing system                    |  |

| IOEMAC0  | 0x180000 | Access to host interface of EMAC 0 and EMAC 1 |  |

| IOEMAC2  | 0x1C0000 | Access to host interface of EMAC 2 and EMAC 3 |  |

| IOTX0    | 0x200000 | Access to configuration of transmit engine 0  |  |

| IORX0    | 0x280000 | Access to configuration of receive engine 0   |  |

| IOTX1    | 0x300000 | Access to configuration of transmit engine 1  |  |

| IORX1    | 0x380000 | Access to configuration of receive engine 1   |  |

| IOTX2    | 0x400000 | Access to configuration of transmit engine 2  |  |

| IORX2    | 0x480000 | Access to configuration of receive engine 2   |  |

| IOTX3    | 0x500000 | Access to configuration of transmit engine 3  |  |

| IORX3    | 0x580000 | Access to configuration of receive engine 3   |  |

| IOADC    | 0x800000 | Access to configuration of input section      |  |

| IODAC    | 0×900000 | Access to configuration of output section     |  |

#### Table 12: IO space layout in the management processor.

The layout of the IO space is shown in Table 12. The configuration for the transmit and receive configuration regions are described in the uplink section. The configuration IO block is described in Table 13.

#### Table 13: Layout of the configuration IO space.

| Configuration Word | Offset | Access | Description                                                                                                                                                                                                       |

|--------------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHANNEL_DIR        | 0x0000 | R/W    | Determines the direction of IO channels S1 to S28. S1<br>is mapped to bit 0. Writing a one into the corresponding<br>bit location will make this an input channel, whereas a<br>zero indicates an output channel. |

|                    |        |        | Bit 31 is used as a soft reset.                                                                                                                                                                                   |

#### Table 13: Layout of the configuration IO space.

| 0x0004                  | R/W                                                                                                                                                                                                                                                                                                                                                           | The LEDs are mapped to bits 0 through 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                                                                                                                                                                                                                                                                                                               | The chip selects for the SPI interface are using bit 8 through 11; these 4 bits are decoded into 16 select lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x0008                  | R                                                                                                                                                                                                                                                                                                                                                             | The dip switches are mapped into bits 0 through 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x080000<br>0x080004    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter values for drawing number of board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x080008<br>0x08000C    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for revision number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x080010<br>0x080014    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for sub revision number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x080018<br>0x08001C    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for board serial number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x080020<br>0x080024    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for ethernet address of EMAC 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x080028<br>0x08002C    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for ethernet address of EMAC 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x080030<br>0x080034    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for ethernet address of EMAC 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x080038<br>0x08003C    | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for ethernet address of EMAC 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x080040 to<br>0x08007C | R/W                                                                                                                                                                                                                                                                                                                                                           | XML decoded parameter value for user tags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0×100000                | R                                                                                                                                                                                                                                                                                                                                                             | Bit 0: Signal detect of the timing signal fiber transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0.100000                |                                                                                                                                                                                                                                                                                                                                                               | Bits 1 through 4: 1 PSS error code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x100008                | R                                                                                                                                                                                                                                                                                                                                                             | GPS time (seconds).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x00000C                | R                                                                                                                                                                                                                                                                                                                                                             | GPS time (fractional part).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |